12. Register Descriptions

271

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

BS:

The block size specifies the size of the image, address lines compared and address lines translated.

END[1:0]

R/W

P1_RST

0b10

Endian Conversion Mode

This bit sets the endian conversion mode. This field is only

applicable if the destination is the Processor Bus.

00 = Little-endian

01 = PowerPC little-endian

10 = Big-endian

11 = True little-endian

MRA

R/W

P1_RST

0

PCI Memory Read Alias to Memory Read Multiple

0 = Disabled

1 = Enabled

When set, the PCI x Target Image X alias a PCI Memory

Read cycle to a PCI Memory Read Multiple cycle and

prefetches the number of bytes specified in the RD_AMT[2:0]

field. When MRA is cleared the Target Image prefetches 8

bytes when a PCI Memory Read command is decoded.

RD_AMT[2:0]

R/W

P1_RST

0

Prefetch Size

Specifies the number of bytes the device prefetches for PCI

Memory Read Multiple transactions claimed by the target

image (see

).

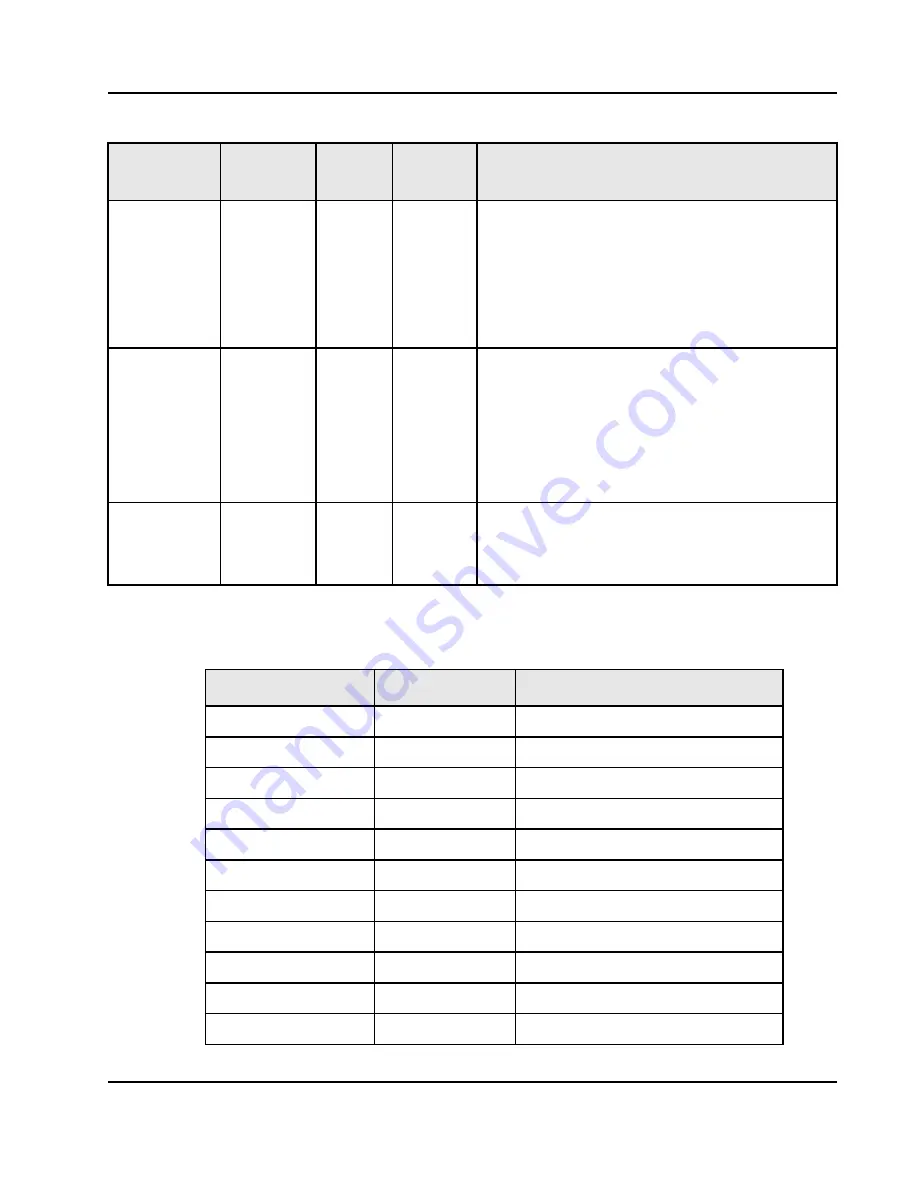

Table 67: Block Size

BS[3:0]

Block Size

Address Lines Compared/Translated

0000

64k

AD31-AD16

0001

128K

AD31-AD17

0010

256K

AD31-AD18

0011

512K

AD31-AD19

0100

1M

AD31-AD20

0101

2M

AD31-AD21

0110

4M

AD31-AD22

0111

8M

AD31-AD23

1000

16M

AD31-AD24

1001

32M

AD31-AD25

1010

64M

AD31-AD26

Name

Type

Reset

By

Reset

State

Function