12. Register Descriptions

304

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

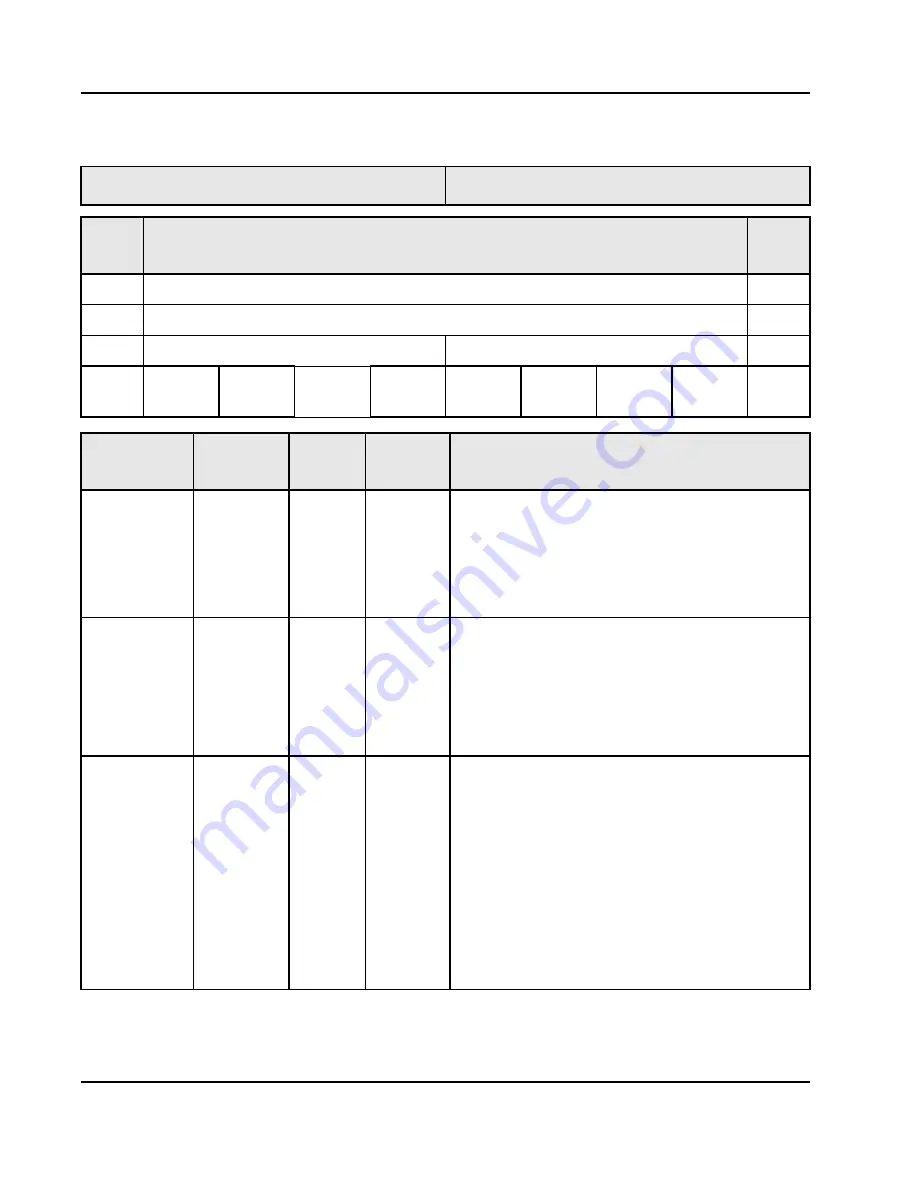

12.5.33

Processor Bus Miscellaneous Control and Status Register

Register Name: PB_MISC_CSR

Register Offset: 0x2C0

PCI

Bits

Function

PB

Bits

31-24

PowerSpan II Reserved

0-7

23-16

PowerSpan II Reserved

8-15

15-08

PowerSpan II Reserved

MAX_RETRY

16-23

07-00

EXT

CYC

MAC_

TEA

MODE_

7400

TEA_EN

ARTRY_

EN

DP_EN

AP_EN

PARITY

24-31

Name

Type

Reset

By

Reset

State

Function

MAX_RETRY

[3:0]

R/W

PB_RST

0

Maximum number of retries. Except for 0000, all entries are

multiples of 64 retries

0000 = retry forever

0001 = 64 retries

0010 = 128 retries

0011 = 192 retries, etc.

EXTCYC

R/W

PB_RST

0

Determines if the PowerSpan II PB master is enabled to

generate extended cycles (16 byte or 24 byte)

This ability improves performance of PowerQUICC II

systems. The EXTCYC bit must be set to 0 in order to ensure

compatibility with WinPath and other PowerPC devices.

0 = Cannot generate extended cycle

1= Can generate extended cycle

MAC_TEA

R/W

PB_RST

1

Master-Abort Configuration Error Mapping

This bit controls the handling of a Master-Abort while a

PowerSpan II PCI Master is generating a configuration

transaction initiated by a processor bus master. If MAC_TEA

is cleared, the processor bus slave returns all ones to the

initiating processor bus master. If MAC_TEA is cleared and

TEA_EN is set to 1, the processor bus slave asserts

PB_TEA_ to terminate the transaction initiated by the

processor.

0 = Assert PB_TEA_ when Master-Abort occurs on PCI

configuration cycles

1 = Return all “1s” when Master-Abort occurs on PCI

configuration cycles