12. Register Descriptions

308

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

Mx_EN

: When set, the arbiter recognizes address bus requests for this master. When cleared, the

arbiter ignores address bus requests from this master. The default state for these bits is determined by

the PWRUP_BOOT option as defined by

:

BM_PARK

: Identifies the master to be parked (see

).

PARK

R/W

PB_RST

0

Bus Park Mode

When set, the arbiter parks the address bus on the Processor

Bus master programmed in the BM_PARK field. When

cleared, the arbiter parks the address bus on the last

Processor Bus master to be granted the bus.

0 = Park on last bus master

1 = Park on specific master

BM_PARK

R/W

PB_RST

0

Bus Master to be Parked

Identifies the master to be parked (see

).

00 = PowerSpan II

01 = External Master 1

10 = External Master 2

11 = External Master 3

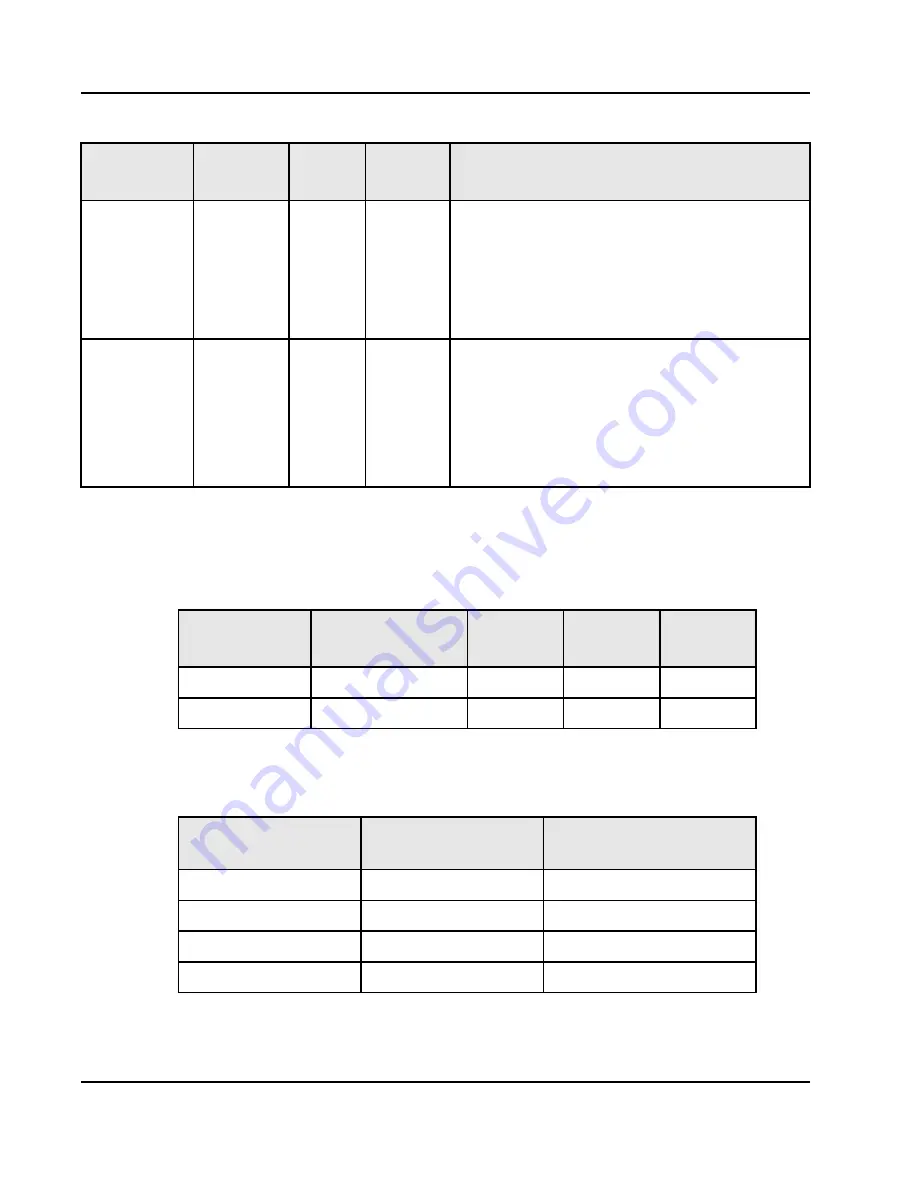

Table 78: Mx_EN Default State

PWRUP_BOOT

Selection

RST_CSR Register

M1_EN

M2_EN

M3_EN

Boot PCI

PCI_BOOT=1

0

0

0

Boot Processor Bus

PCI_BOOT=0

1

0

0

Table 79: Parked Processor Bus Master

BM_PARK [1:0]

Parked Processor Bus

Master

External Pins

00

PowerSpan II

None

01

M1

PB_BR[1]_/PB_BG[1]_

10

M2

PB_BR[2]_/PB_BG[2]_

11

M3

PB_BR[3]_/PB_BG[3]_

Name

Type

Reset

By

Reset

State

Function