12. Register Descriptions

314

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

12.5.39

DMA x General Control and Status Register

This register contains general control and status information for channel DMA

x

. This register is not

part of a linked-list Command Packet..

Writing to the CHAIN and OFF bits while the DMA is active has no effect.

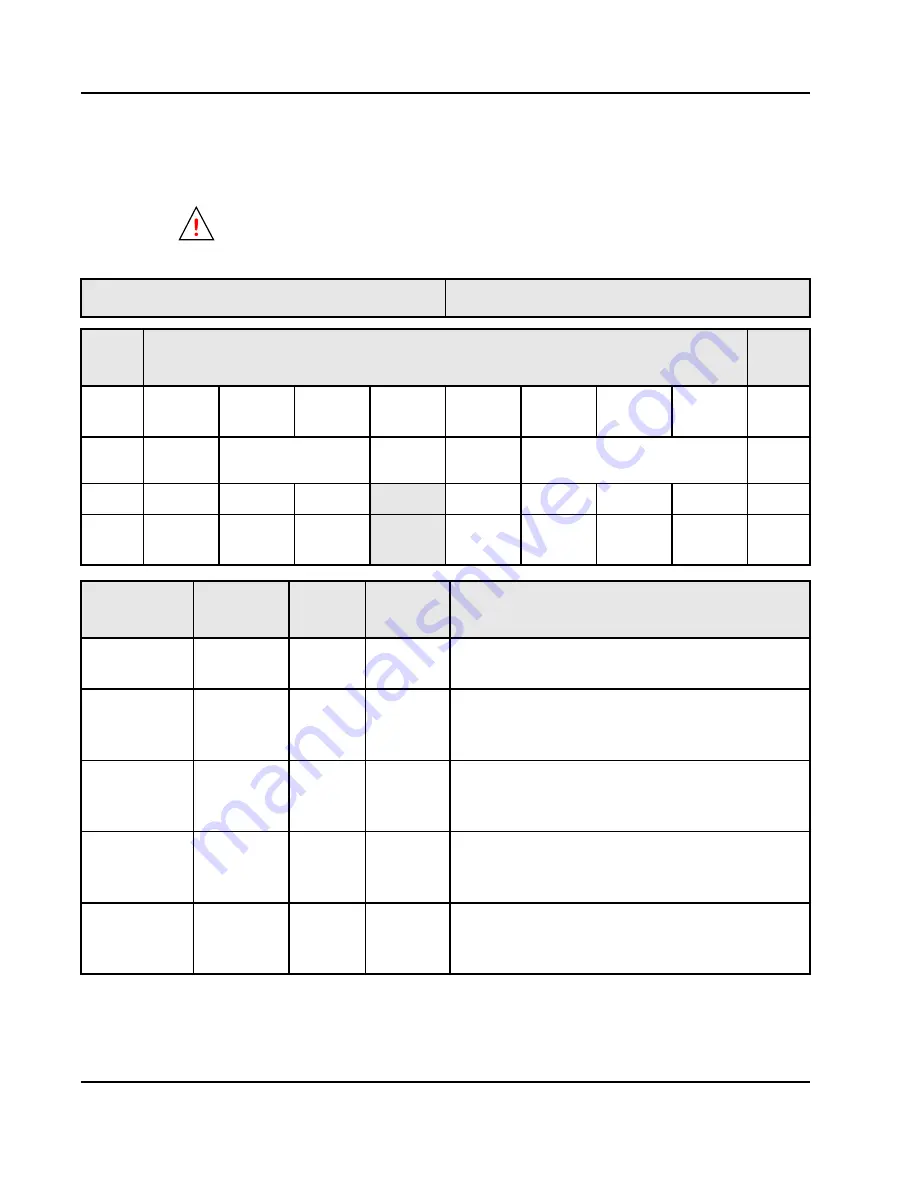

Register Name: DMAx_GCSR

Register Offset: 0x320, 0x350, 0x380, 0x3B0

PCI

Bits

Function

PB

Bits

31-24

GO

CHAIN

0

0

0

STOP_

REQ

HALT_

REQ

0

0-7

23-16

DACT

DBS

DBS_

EN

OFF

8-15

15-08

0

0

P1_ERR

P2_ERR

PB_ERR

STOP

HALT

DONE

16-23

07-00

0

0

P1_ERR_

EN

P2_ERR_

EN

PB_ERR_

EN

STOP_

EN

HALT_

EN

DONE_E

N

24-31

Name

Type

Reset

By

Reset

State

Function

GO

Write 1 to Set

G_RST

0

DMA Go bit

0 = no effect, 1 = Begin DMA transfer

CHAIN

R/W

G_RST

0

DMA Chaining

0 = DMA Direct mode

1 = DMA Linked-List mode

STOP_REQ

Write 1 to Set

G_RST

0

DMA Stop Request

0 = no effect

1 = Stop DMA when all buffered data has been written

HALT_REQ

Write 1 to Set

G_RST

0

DMA Halt Request

0 = no effect

1 = Halt DMA at completion of current command packet

DACT

R

G_RST

0

DMA Active

0 = not active

1 = active