2. PCI Interface

64

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

— Configure address translation

–

Translation Address Enable (TA_EN) bit in the PCI_TI2O_CTL register.

–

Translation Address (TADDR) in the

“PCI I2O Target Image Translation Address

(PCI_TI2O_TADDR)

— Enable decode in PCI memory space.

–

Set memory Space (MS) bit in the

“PCI-1 Control and Status Register.” on page 251

At this stage, the I

2

O image is defined but all accesses to the PCI I

2

O target image are retried.

4.

The IOP is required to initialize all Top and Bottom Pointer registers and initialize all the MFAs in

the Inbound Free List FIFO. At this point, the IOP enables PCI accesses with the following step:

— Set the I2O Enable (I2O_EN) bit in the

“I2O Control and Status Register” on page 357

2.6.3

Messaging Interface

The

I

2

O 2.0 Specification

defines a mechanism for connecting an I/O Platform (IOP) to an I

2

O system

through a memory-based system, such as PCI, which has no inherent message passing capability. An

IOP which is connected to a memory-based system is said to be locally attached. The PowerSpan II

implements four I

2

O defined memory mapped registers on PCI to enable the physical and logical

connection of the IOP to the system. Two of these memory-mapped registers provide the interface for

the external Host platform and other IOPs to exchange messages with the local IOP sitting behind the

PowerSpan II. These two registers are the Inbound Queue and Outbound Queue interfaces. The other

two registers are used as I

2

O specific Interrupt Status and Enable registers for the local IOP to signal

the Host platform. Additional PowerSpan II specific registers are implemented to support the

messaging interface.

2.6.3.1

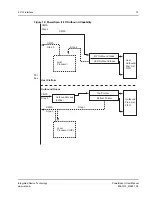

Inbound Queue

The I

2

O Inbound Queue register is the messaging interface used by the Host or external IOP to post

messages to the local IOP.

The I

2

0 Inbound Queue Register Interface is located at offset 0x040 of the PowerSpan II PCI I

2

0 target

image in PCI Memory space. The Inbound Queue has a Free List FIFO and a Post List FIFO, both of

which reside in the IOP local memory.

2.6.3.2

Inbound Free List FIFO and Post List FIFO

The Free List contains the Message Frame Address (MFAs) of Message Frames (MFs) in the IOP’s

local memory, which are available to the Host or other IOPs for writing inbound messages.

The Post List contains the MFAs of MFs in the local IOPs memory which contain inbound messages

for the IOP to process.