2. PCI Interface

68

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

2.6.4

Inbound Messages

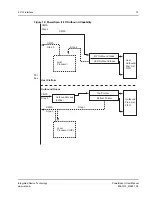

The Inbound Free and Post List FIFOs are implemented as circular queues using Bottom and Top

pointers. The PowerSpan II implements the Bottom and Top pointers for the Inbound Free List FIFO

and the Inbound Post List FIFO. The FIFOs reside in the local memory. The Inbound posted messages

also reside in local processor memory.

When the Host platform or external IOP wants to post a message to the local IOP, it must first acquire

an MFA from the Inbound Free List. This is accomplished through a PCI read transaction to the

PowerSpan II Inbound Queue Register at offset 0x040 of the I

2

O target image. PowerSpan II provides

the next available MFA from the Inbound Free List FIFO pointed to by the Inbound Free List Bottom

Pointer Register. PowerSpan II increments the Inbound Free List Bottom Pointer Register to point to

the next entry of the FIFO. A read from the Inbound Queue Register when the Inbound Free List FIFO

is empty (Bottom Pointer equal to Top pointer) returns 0xffff_ffff to the requesting PCI master.

Once the Host or external IOP obtains an MFA, it is then to write a message to the IOP’s local MF at

the address offset from the Px_BSI2O specified by the MFA. Once the message is transferred the Host

or external IOP writes the MFA back to the same I

2

O target image offset (0x040). PowerSpan II

accepts the write transaction on PCI and generate a write to the Inbound Post List FIFO at the local IOP

memory address pointed to by the Inbound Post List Top Pointer Register. PowerSpan II then

increments the Inbound Post List Top Pointer Register and asserts the I2O_IOP Interrupt Status bit in

the ISR0 register to notify the local processor of MFAs in the Inbound Post list FIFO. The IPL bit in the

“I2O Control and Status Register” on page 357

is set while the Inbound Post List FIFO is not empty,

indicating that Inbound Message Frames need to be processed.

2.6.4.1

Local Processor Functions

For Inbound Messaging, the local processor performs the following:

•

detects the interrupt

•

reads the PowerSpan II ISR0 Register

•

determines the source of the interrupt through the I2O_IOP register

•

clears the I2O_IOP interrupt (write 1 to clear)

•

reads the Inbound Post List FIFO Bottom Pointer Register to access the Inbound Post List FIFO to

get the MFA

•

increments the Inbound Post List Bottom Pointer Register by writing the Inbound Post List Bottom

Pointer Increment Register

•

reads and processes the MF pointed to by the MFA

•

writes the MFA back to the Top of the Inbound Free List FIFO

•

writes to the PowerSpan II’s Inbound Free List Top Pointer Increment Register to increment the

address by four

•

reads the IPL bit, in the I2O_CSR, to determine if the Inbound Post List is empty

The interrupt can be masked, leaving it to the processor to poll the ISR Register. A read from the

Inbound Post List Bottom Pointer Register by the IOP when the Inbound Post List FIFO is empty

returns 0xffff_ffff to the processor if the EMTR field of the I2O_CSR register is set to one.