83

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

3.

Processor Bus Interface

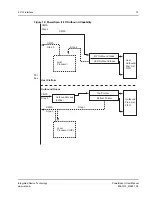

This chapter describes the functionality of the Processor Bus Interface. Both the Single PCI PowerSpan

II and Dual PCI PowerSpan II have a Processor Bus Interface. The following topics are discussed:

•

•

“PB Slave Interface” on page 84

•

“PB Master Interface” on page 100

3.1

Overview

The PowerSpan II Processor Bus (PB) Interface directly connects with a wide range of processors in

order to meet the demands of high end systems, the PB Interface operates up to100 MHz and has a

64-bit data bus.

3.2

Interface Support

The PowerSpan II Processor Bus Interface supports the following embedded processors:

— Motorola: PowerQUICC II (MPC825x, MPC826x, MPC827x, MPC8280), PowerPC 7XX

(MPC74x, MPC75x), PowerPC 7400

— IBM: PowerPC 740, PowerPC 750

— Wintegra: WinPath

TM

Although these interfaces are not identical, for the most part the processor interface on the PowerSpan

II is referred to simply as the Processor Bus (PB). The interface sections in this chapter highlight where

the PowerSpan II operates differently to address specific processor requirements as the need arises. An

example of this different operation is the extended cycles with the PowerQUICC II.

3.2.1

Terminology

The following terms are used in the Processor Bus Interface descriptions:

•

Address retry window

: refers to the clock following the assertion of AACK_, which is the latest a

snooping master can request for an address tenure re-run.

•

Window of opportunity:

refers to the clock following the assertion of ARTRY_. The retrying

master has to request the bus on this clock to ensure that it is the next bus owner. This enables it to

perform the transactions required to maintain cache coherency.

The PowerQUICC II and PowerPC 7400 must operate in 60x compatible bus mode to be used

with PowerSpan II. In single PowerQUICC II mode the processor cannot share the bus with

other external masters.