3. Processor Bus Interface

88

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

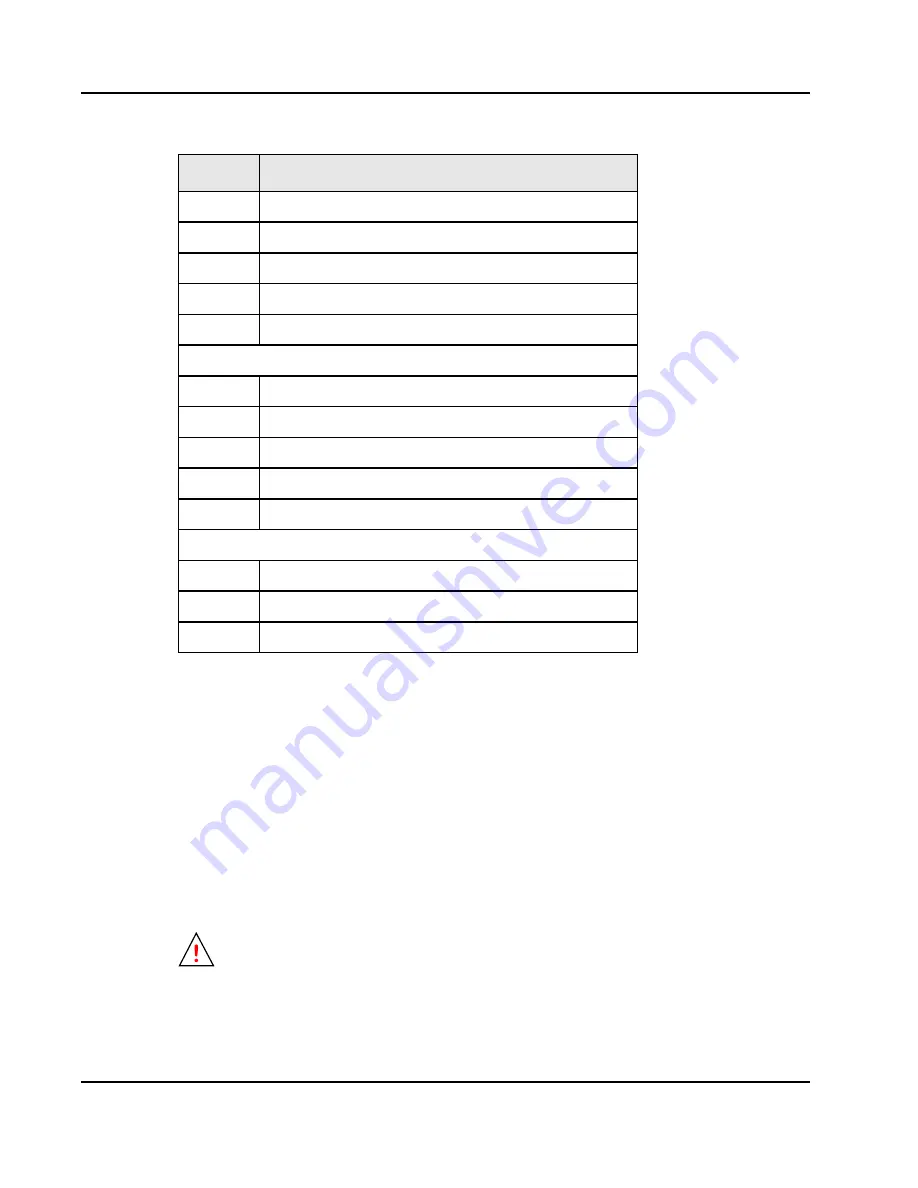

Because PowerSpan II does not have a cache, all read and write transfer types are treated the same. For

example, a Read with Intent to Modify command (PB_TT= 01110) is handled the same way as a Read

Atomic command (PB_TT= 11010).

PowerSpan II performs PCI read prefetches and stores read data in an internal buffer when the Prefetch

Keep (PRKEEP) bit is set to 1. The purpose of a prefetch read is to fetch read information before the

master requests the information. If the master then requests the information the target can respond

immediately with the prefetched information. This ability protects the master from slow access times

for information it requires. However, when a write is performed to a prefetched address, a subsequent

read could yield stale data. In order to guarantee there is no stale data, set the PRKEEP bit to 0. This

function disables the internal buffer to ensure there is no stale data. By setting this PRKEEP bit to 0

PowerSpan II is unable to perform PCI read prefetches and read performance may be decreased in the

system.

10000

eieio

11000

tlb invalidate

00001

lwarx

01001

tlb sync

01101

icbi

Reads

01010

Read

01110

Read with intent to modify

11010

Read Atomic

11110

Read with intent to modify atomic

01011

Read with no intent to cache

Writes

00010

Write with flush

00110

Write with kill

10010

Write with flush atomic

Prefetching attributes for each image map must meet the system’s cache coherency

requirements

Table 13: PowerSpan II PB Slave Transfer Types

TT[0:4]

Name