3. Processor Bus Interface

92

PowerSpan II User Manual

80A1010_MA001_09

Integrated Device Technology

www.idt.com

3.3.2

Data Phase

The data phase deals with the control of transaction length.

3.3.2.1

Transaction Length

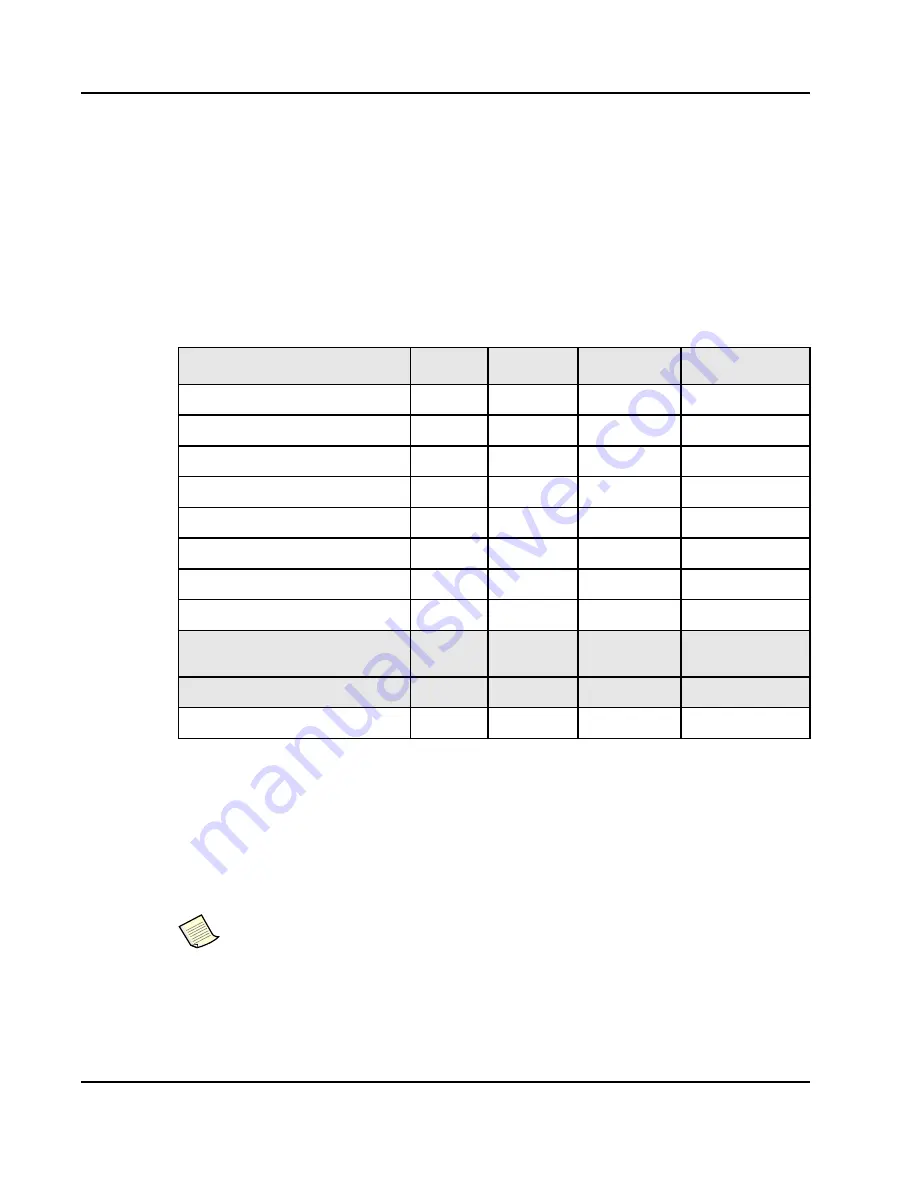

The PB Slave supports a set of the data transfer sizes supported by the embedded PowerPC family. All

data transfer sizes supported by the PowerSpan II PB Slave are illustrated in

. Burst transfers

are indicated by the assertion of Processor Bus Transfer Burst (PB_TBST_). The shaded regions

indicate transaction sizes unique to the PowerQUICC II.

3.3.2.2

Data Alignment

Embedded processor bus transfer sizes and alignments, defined in

and

, are supported

by the PB Slave for transaction accesses. The shaded table cells in

show transactions that

support the

PowerPC 7400

processor.

lists the size and alignment transactions less than or equal to 8 bytes. PowerSpan II register

accesses are limited to 4 bytes or less.

Table 16: PowerSpan II PB Transfer Sizes

Transfer Size

Bytes

PB_TBST

PB_TSIZ[0]

PB_TSIZ[1:3]

Byte

1

1

0

001

Half-word

2

1

0

010

Tri-byte

3

1

0

011

Word

4

1

0

100

Five bytes

5

1

0

101

Six bytes

6

1

0

110

Seven bytes

7

1

0

111

Double Word (DW)

8

1

0

000

Extended Double (PowerQUICC II

only)

16

1

1

001

Extended Triple (PowerQUICC II only)

24

1

1

010

Burst (Quad DW)

32

0

0

010

The PowerSpan II port size is 64-bit.