11

Tsi340 Evaluation Board User Manual

80E3000_MA002_02

Integrated Device Technology

www.idt.com

3. Board

Layout

In the board layout section of this document the component placement and the setting options are

explained.

3.1

PCB Layers

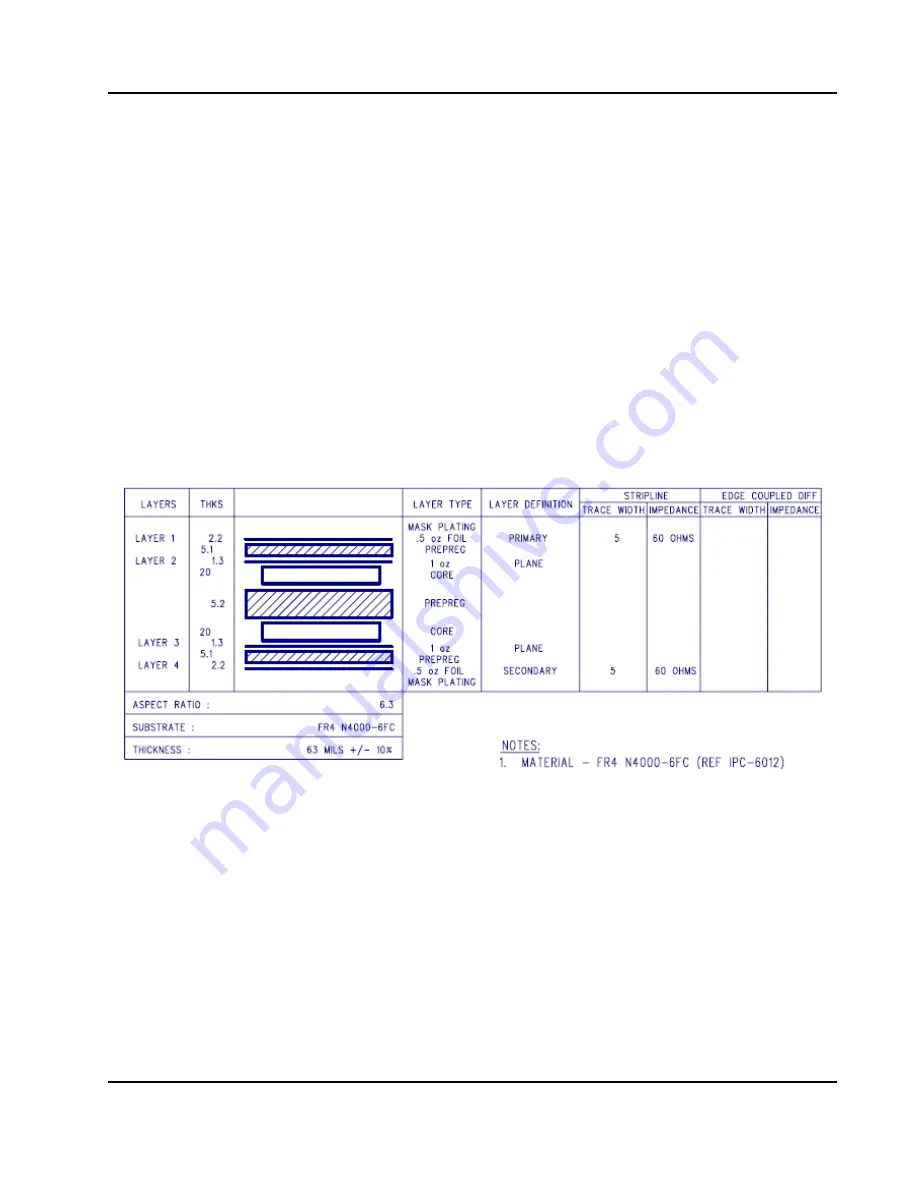

The Tsi340 Printed Circuit Board (PCB) stack up is made of the following four layers:

•

Layer 1: PCB primary side (where most traces are routed)

•

Layer 2: Ground plane

•

Layer 3: Power plane

•

Layer 4: Secondary side

Figure 4

shows the four layers of the PCB.

Figure 4: PCB Stack Up