1. Board Design

9

Tsi381 Evaluation Board User Manual

60E2000_MA001_03

Integrated Device Technology

www.idt.com

1.2

PCI Interface

1.2.1

Overview

The PCI Interface is implemented on the board with four slots, in which one is an R/A mounted

connector on the top of the board. All PCI connectors are compliant with the PCI 3.0 specification.

Appropriate clearance is provided such that up to four PCI cards can be inserted for testing while the

board is in an open-chassis standard ATX case.

The PCI Interface supports four slots operating at 25, 33, 50, or 66 MHz.

1.2.2

IDSEL Signals

IDSEL signals are connected in the following order:

•

Slot 0 – R/A connector top slot: 150 ohms to AD16 (Device 0)

•

Slot 1 – 150 ohms to AD17 (Device 1)

•

Slot 2 – 150 ohms to AD19 (Device 3)

•

Slot 3 – 150 ohms AD18 (Device 2)

1.2.3

Interrupt Signals

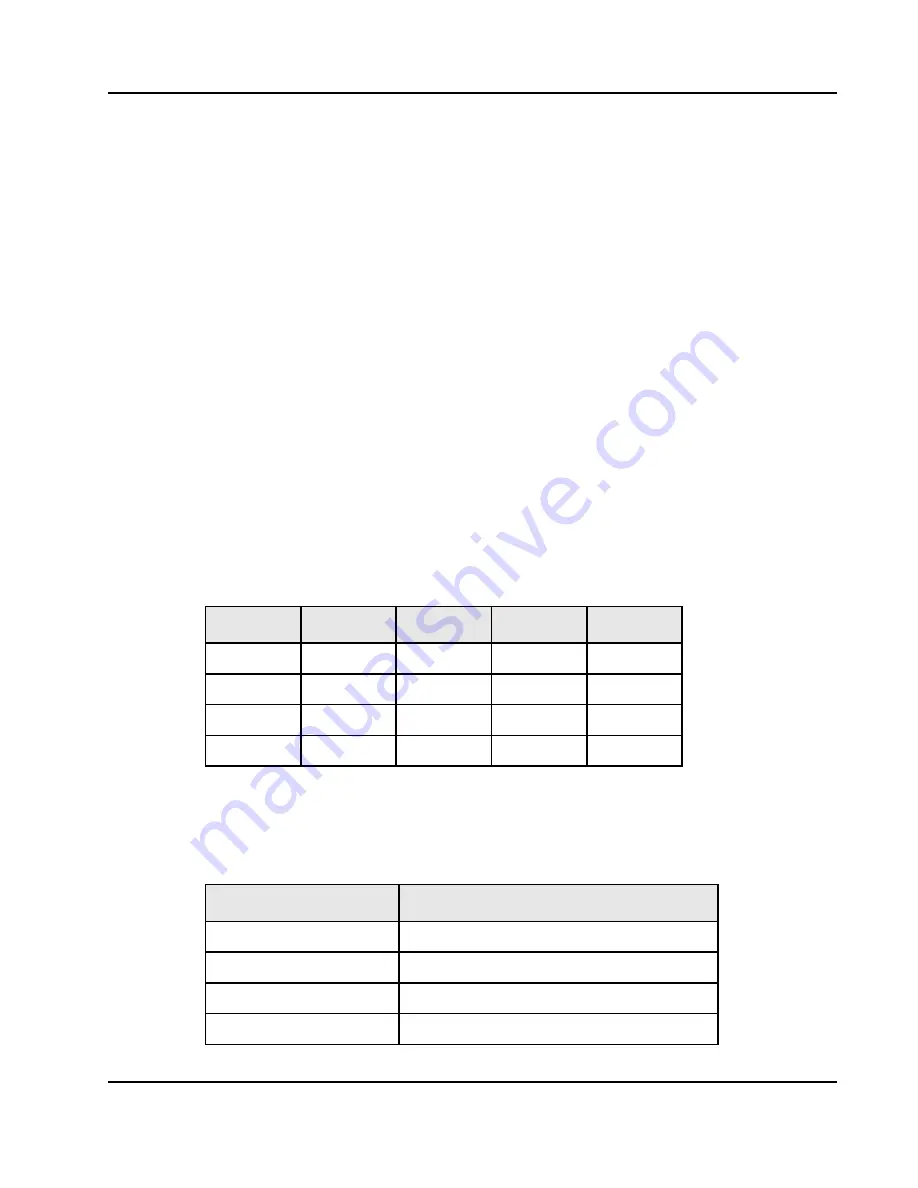

The PCI interrupt signals are connected to the slots as shown in the following table.

1.2.4

Pull-up Signals

The following pull-ups are added to the PCI bus, in which a value of 8.2Kohm is used.

Table 1: PCI Interrupt Routing

Tsi381

Slot 0

Slot 1

Slot 3

Slot 4

A

A

B

D

C

B

B

C

A

D

C

C

D

B

A

D

D

A

C

B

Table 2: PCI Pull-up Signals

Signal

Description

PCI_REQ#[0:3]

Bus request

PCI_GNT#[0:3]

Bus grant

PCI_FRAME#

Control signal

PCI_IRDY#, PCI_TRDY#

Control signal