Industrial Electronic Engineers, Inc.

SIZE

A

CODE IDENT

NO.

05464

S03875–06–0114

Van Nuys, California

Scale: NONE

Rev A

Sheet 7

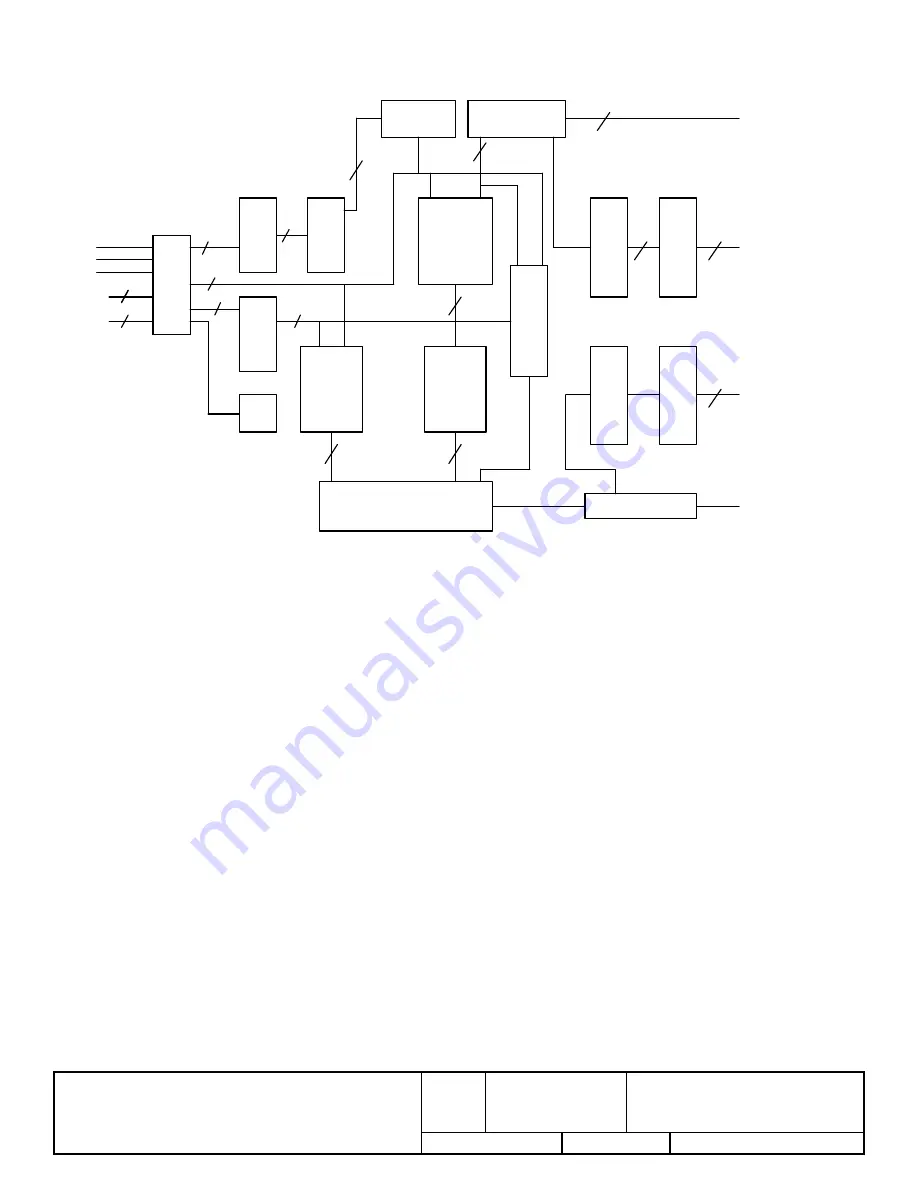

2.2

LCD Controller

DB4–DB7

E

R/W

RS

DB0–DB3

4

4

I/O Buffer

Instruction

Decoder

Instruction

Register (IR)

Data

Register (DR)

Busy

Flag

I/O Buffer

8

Character

Generator

RAM

(CG RAM)

512 Bits

Cursor Blink

Control Circuit

Display Data

RAM

(DD RAM)

80x8 bits

8

8

8

Character

Generator

ROM

(CG ROM)

7200 Bits

8

7

7

Timing Generation

Circuit

Address

Counter (AC)

7

Common Signal

Driver

16–bit Shift

Register

3

16

16

CL1

CL2

M

Parallel/Serial Data

Conversion Circuit

(Parallel Data –Serial Data)

40–bit Latch

Circuit

Segment Signal

Driver

40–bit Shift Register

Seg1–Seg40

Com1–Com16

D

5

5

40

Figure 2

LCD Controller Block Diagram

2.2.1

Instruction Register (IR)

The IR stores instruction codes such as display clear and cursor shift, and address information of the display

data RAM (DD RAM) and character generator RAM (CG RAM). The IR can be written from the MPU, but not

read.

2.2.2

Data Register (DR)

The DR temporarily stores data to be written into or read from the DD RAM or the CG RAM.

2.2.3

Busy Flag

When the Busy Flag is a "1", the module is in an internal operating mode and ignores any additional instructions

(Refer to Read Busy Flag and Address instruction).

2.2.4

Address Counter (AC)

The AC determines the address of the DD RAM or CG RAM in which new data is stored. After writing into (or

reading from) the DD RAM or CG RAM, the AC is incremented or decremented as defined by the

Increment/Decrement bit (Refer to Entry Mode Set instruction).

2.2.5

Display Data RAM (DD RAM)

The DD RAM contains 80 X 8 bits and represents 80 characters. The relationship between the DD RAM

address and position of the characters in the display can be controlled by the user (Refer to Entry Mode Set and

Cursor or Display Shift instructions).

2.2.6

Character Generator ROM (CG ROM)

The CG ROM generates character patterns of 5 X 7 dots from 8 bit character codes. The 192 5 X 7 dot matrix