R E M O T E O P E R A T I O N S

Status Reporting

32

LDC-3926339

C H A P T E R

3

summary to generate the interrupt. See the mainframe Instruction Manual for

details about status structures.

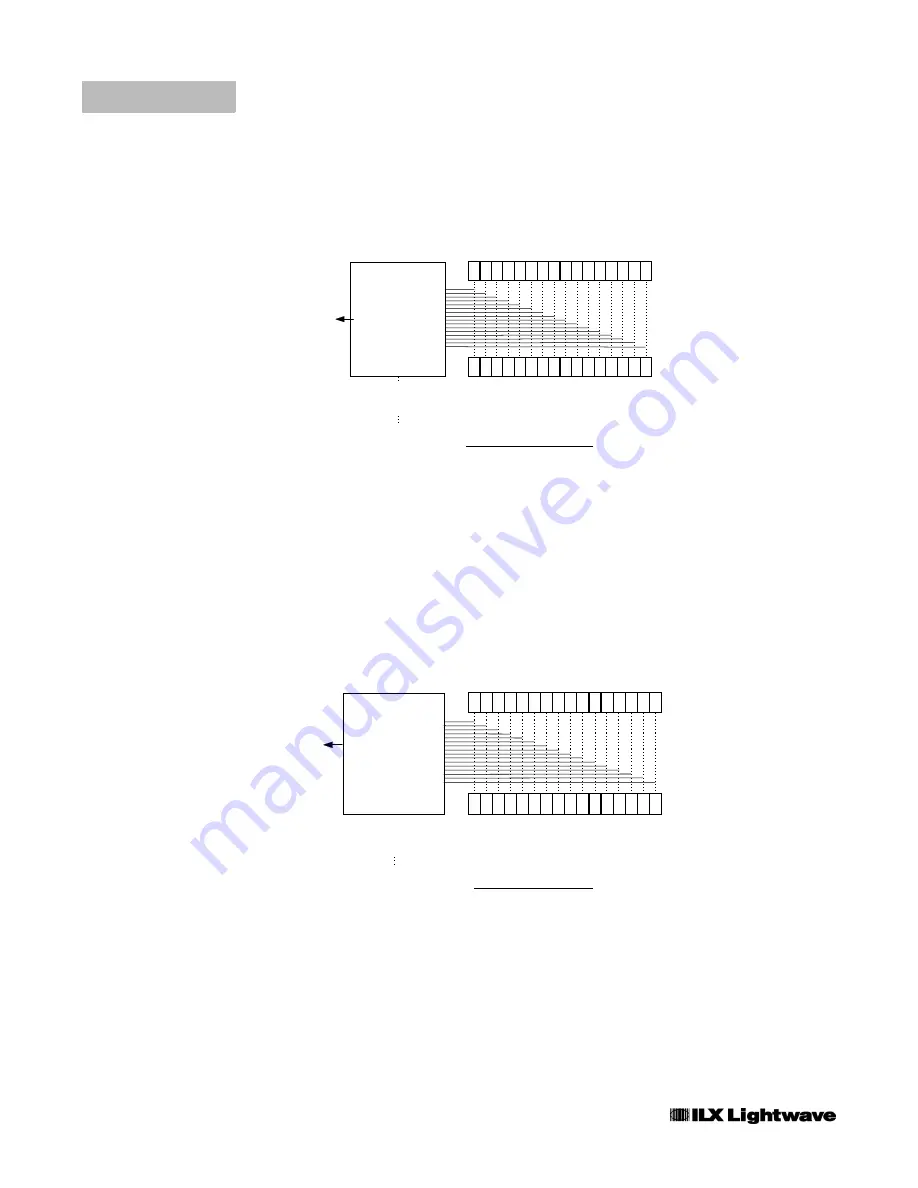

Figure 3.2

Condition Registers

Figure 3.3

Event Registers

bit-wise

LOGICAL AND

LASER Condition Status Register

LASER:COND?

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

LOGICAL OR

LASER Condition Status Enable Register

LASER:ENABle:COND <nrf>

LASER:ENABle:COND?

LASER Condition Bit Reference

0 - Current Limit

8 - Output Shorted

1 - Voltage Limit

9 – In Tolerance

2 - n/a

10 - Output On

3 - Power Limit

11 - n/a

4 - Interlock Error

12 - n/a

5 - n/a

13 - n/a

6 - n/a

14 - n/a

7 - Open Circuit

15 - n/a

To ALLCOND

Register

bit-wise

LOGICAL AND

LASER Event Status Register

LASER:EVEnt?

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

LOGICAL OR

LASER Event Status Enable Register

LASER:ENABle:EVEnt <nrf>

LASER:ENABle:EVEnt?

LASER Event Bit Reference

0 - Current Limit

8 - Output Shorted

1 - Voltage Limit

9 – Tolerance Change

2 - n/a

10 - Output On

3 - Power Limit

11 - n/a

4 - Interlock Error

12 - n/a

5 - n/a

13 - n/a

6 - n/a

14 - n/a

7 - Open Circuit

15 - n/a

To ALLEVE

Register

Artisan Technology Group - Quality Instrumentation ... Guaranteed | (888) 88-SOURCE | www.artisantg.com