Video Capture

The video capture engine is responsible for receiving video pixel data and

qualifiers from the on-board video decoder chip, formatting the data and

transferring it into on-board memory. The data that it receives from the

video decoder is 4:2:2 YCrCb data formatted per Table 1. The video

decoder delivers 8 bits of Luminance data ( Y ) and 8 bits of Chrominance

data ( Cr/Cb ).The video capture engine translates this data into longwords

( 32 bits ) as defined in Table 2. This format reflects how the data will

appear in host memory. The module packs two pixels into each longword

in order to use the Cardbus bandwidth more efficiently and conserve

memory space.

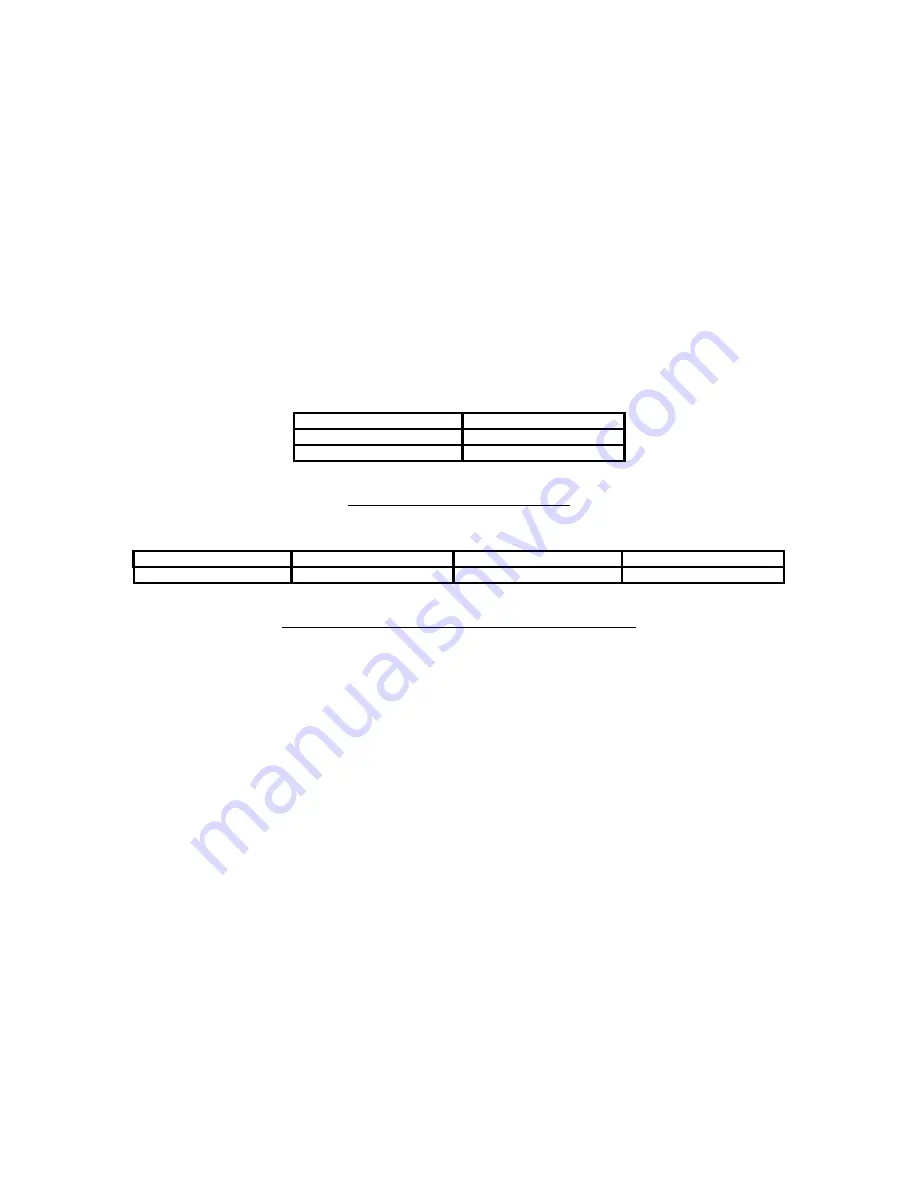

H-Port I-Port

d15 d14 d13 d12 d11 d10 d9 d8 d7 d6 d5 d4 d3 d2 d1 d0

Cr/Cb ( chrominance )

Y ( luminance )

Table 1 – Video decoder pixel data

d31 d30 d29 d28 d27 d26 d25 d24 d23 d22 d21 d20 d19 d18 d17 d16 d15 d14 d13 d12 d11 d10 d9 d8 d7 d6 d5 d4 d3 d2 d1 d0

Cr/Cb-pixel2 Y-pixel2 Cr/Cb-pixel1 Y-pixel1

Table 2 – VCE-PRO Image data mapping into memory

Pixel Buffering

The pixel data formatted by the video capture engine is stored into two

on-board 4Mx32 SDRAM devices. This memory serves as a local store for

formatted video pixel data. Each SDRAM will buffer a single frame’s

worth of data, supporting a maximum frame size of 8 million pixels/frame.

The SDRAMs are managed by an independent pair of controllers,

implemented in the FPGA, supporting concurrent operation. The two

SDRAMs are utilized in a ping-pong fashion such that while one is being

filled with new pixel data, the other is being emptied via DMA into host

memory.

DMA

The DMA engine is responsible for reading formatted pixel data from the

on-board SDRAM devices and transferring them into host memory via the

Cardbus interface. An intelligent scatter-gather method is utilized,

providing for an efficient use of the Cardbus bandwidth. The use of non-

contiguous 4Kbyte buffers provides support for the Windows operating

system’s memory allocation model.

Page

9 of 44