XC2200 Derivatives

System Units (Vol. 1 of 2)

Central Processing Unit (CPU)

User’s Manual

4-64

V2.1, 2008-08

CPUSV2_X, V2.2

4.9

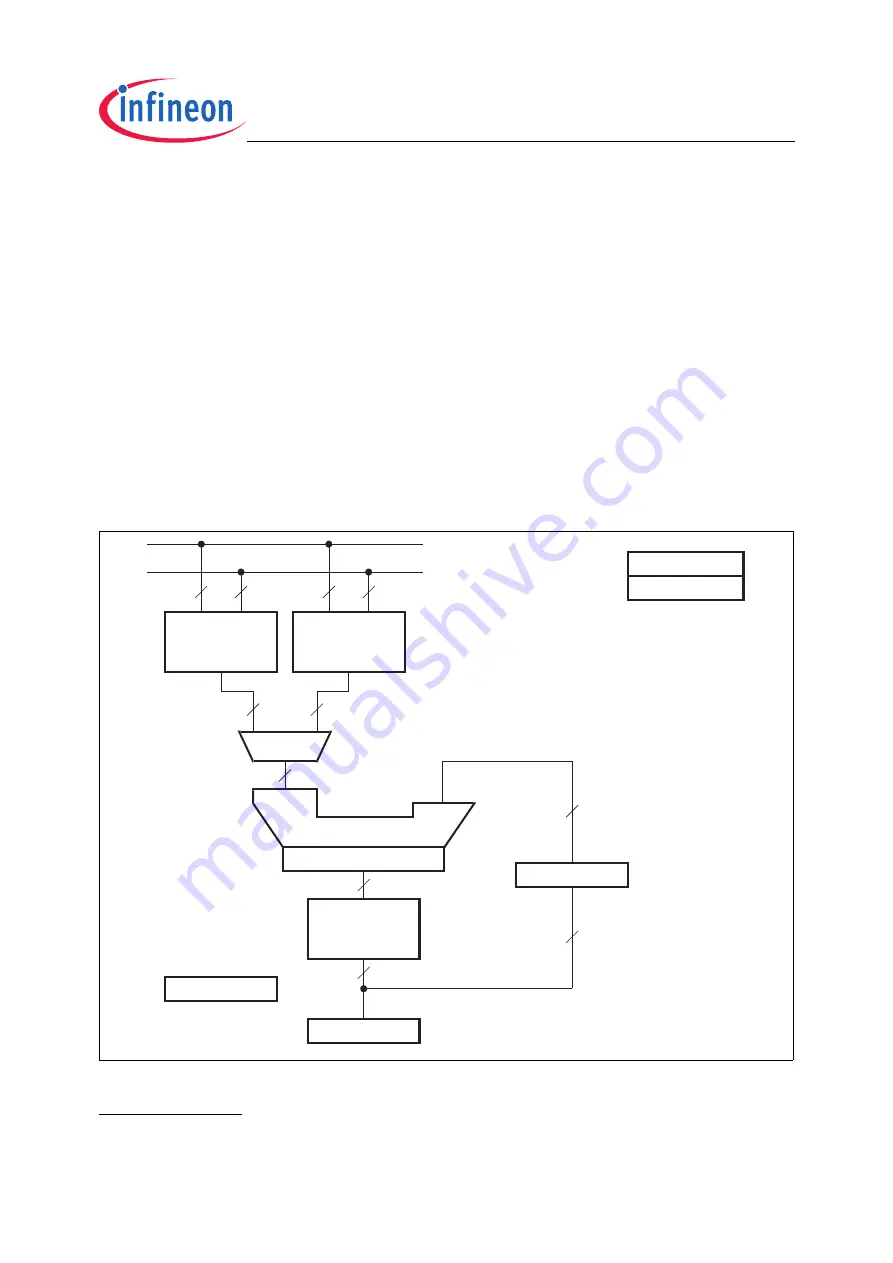

DSP Data Processing (MAC Unit)

The new CoXXX arithmetic instructions are performed in the MAC unit. The MAC unit

provides single-instruction-cycle, non-pipelined, 32-bit additions; 32-bit subtraction; right

and left shifts; 16-bit by 16-bit multiplication; and multiplication with cumulative

subtraction/addition. The MAC unit includes the following major components, shown in

•

16-bit by 16-bit signed/unsigned multiplier with signed result

1)

•

Concatenation Unit

•

Scaler (one-bit left shifter) for fractional computing

•

40-bit Adder/Subtracter

•

40-bit Signed Accumulator

•

Data Limiter

•

Accumulator Shifter

•

Repeat Counter

Figure 4-18 Functional MAC Unit Block Diagram

1) The same hardware-multiplier is used in the ALU.

MCA04930

40-Bit Adder/Subtracter

Signed

Ext.

Round + Saturation

32

Signed/

Unsigned

Multiplier

Concatenation

Unit

32

32

16

16

16

16

16-Bit Input Operands

40

40-Bit Signed

Accumulator

Limiter

40

ACCU-Shifter

40

40

MSW Register

Repeat Counter

MCW Register