XC2200 Derivatives

System Units (Vol. 1 of 2)

Startup Configuration and Bootstrap Loading

User’s Manual

10-3

V2.1, 2008-08

SCFG/BSL, V1.3

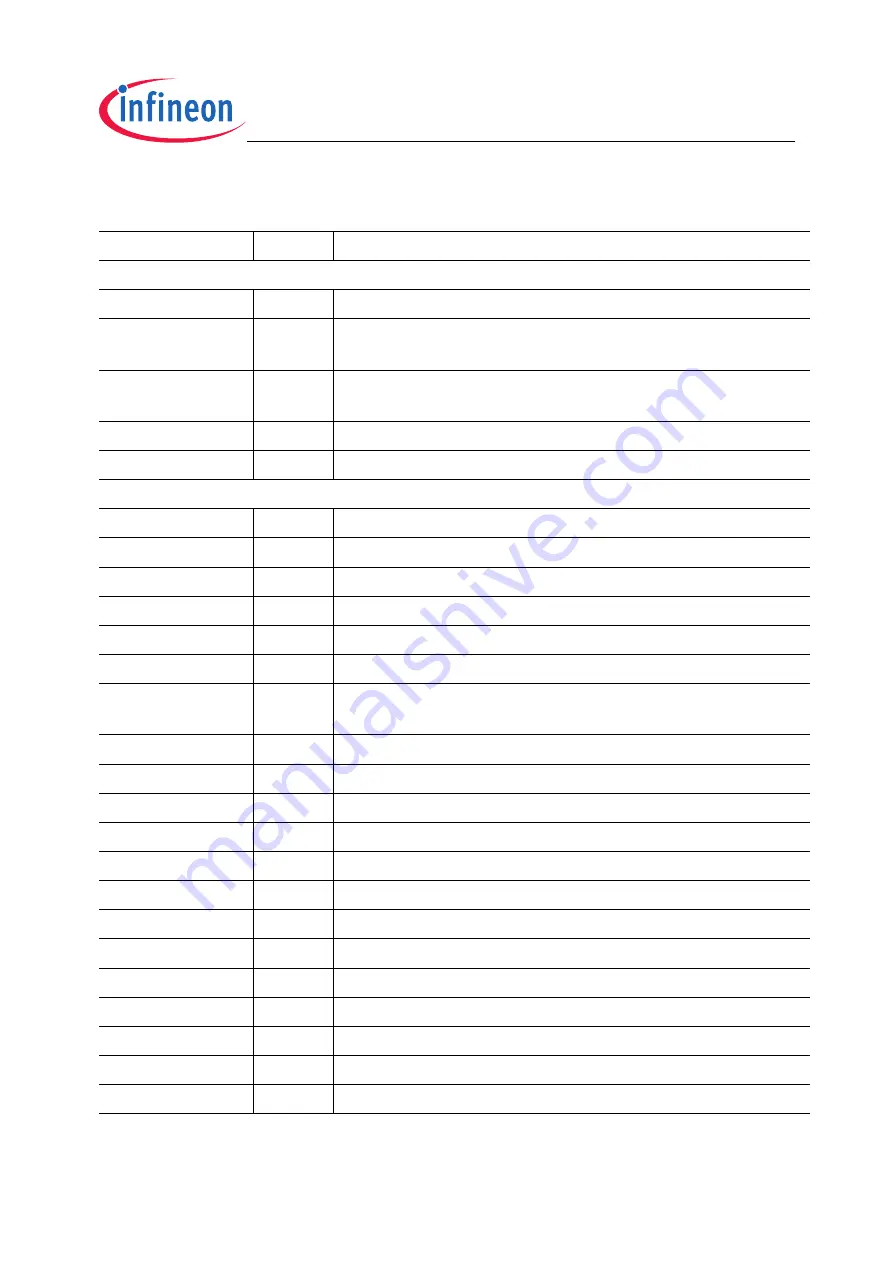

Table 10-2

XC2200 Registers installed by the Start-Up Procedure

Register

Value

Comments

1. After any start-up:

TRAPDIS

009F

H

All SCU-controlled traps disabled except PET and RAT

RSTCON1

UU:

11

uu:U

H

Application Reset request generated by WDT

WDTCS

UUU:

uuu

0

H

Overflow Error Status is reset ; the original flag is saved in

(refer to

TRAPDIS

009F

H

All SCU-controlled traps disabled except PET and RAT

PMTSR

0100

H

Parity Error Sensitivity Enabled

2. After power-on in DMP_1:

PLLCON0

0F00

H

PLL in Normal Mode, N-divider = 16

PLLCON1

000A

H

Internal clock as input for PLL

PLLCON2

0000

H

K1-divider = 1

PLLCON3

8007

H

K2-divider = 8

SYSCON0

0002

H

The PLL output (f

PLL

) used as system clock

WUOSCCON

0000

H

Wake up Oscillator enabled with f

WU

approx. 500kHz

HPOSCCON

U:u

0

uu:

UU

H

PLLSTAT.FINDIS bit will not be set

in an OSCWDT emergency case

PLLOSCCON

XXXX

H

Device-specific value (chip-to-chip trimming)

EVRMCON0

0110

H

EVR_M Control 0 register

EVR1CON0

0D10

H

EVR_1 Control 0 register

EVRMCON1

0101

H

EVR_M Control 1 register

EVRMSET15VHP 001B

H

EVR_1 Setting for 1.5V HP register

EVR1SET15VHP

001B

H

EVR_1 Setting for 1.5V HP register

PVCMCON0

2544

H

PVC_M Control for Step 0 register

PVC1CON0

2544

H

PVC_1 Control for Step 0 register

SWDCON0

0941

H

SWD Control 0 register

EVRMSET10V

005B

H

EVR_M Setting for 1.0V register

EVRMSET15VLP 00DD

H

EVR_M Setting for 1.5V LP register

EVR1SET10V

005B

H

EVR_1 Setting for 1.0V register

EVR1SET15VLP

00DD

H

EVR_1 Setting for 1.5V LP register