CPU_45B-V1

CPU Board XMC4500 SDRAM

Hardware Description

Board User's Manual

22

Revision 1.0, 2013-02-20

2.9

RTC

The XMC4500 CPU has two power domains, the Core Domain and Hibernate Domain.

The Core Domain (VDDP pins) is connected to the VDD3.3 rail. An on-board LDO voltage regulator generates

VDD3.3 (3.3 V) from VDD5 (5 V).

The Hibernate Domain is powered via the auxiliary supply pin VBAT, which is supplied by either a 3 V coin cell

(size 1216, 1220, 1225) plugged into the battery holder or 3.3 V (VDD3.3) generated by the on-board voltage

regulator.

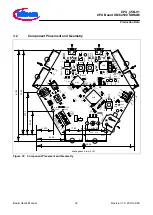

Figure 19

Battery Holder for Coin Cells

The Real Time Clock (RTC) is located in the hibernate domain. The XMC4500 uses the HIB_IO_1 signal (active

low) to shutdown the external LDO voltage regulator which generates VDD3.3 (core domain). Even if the Core

Domain is not powered the Hibernate Domain will operate if VBAT is available. The RTC keeps running as long

as the Hibernate Domain is powered via the auxiliary supply VBAT. The RTC is capable to wake-up the whole

system from Hibernate mode by setting HIB_IO_1 to high.

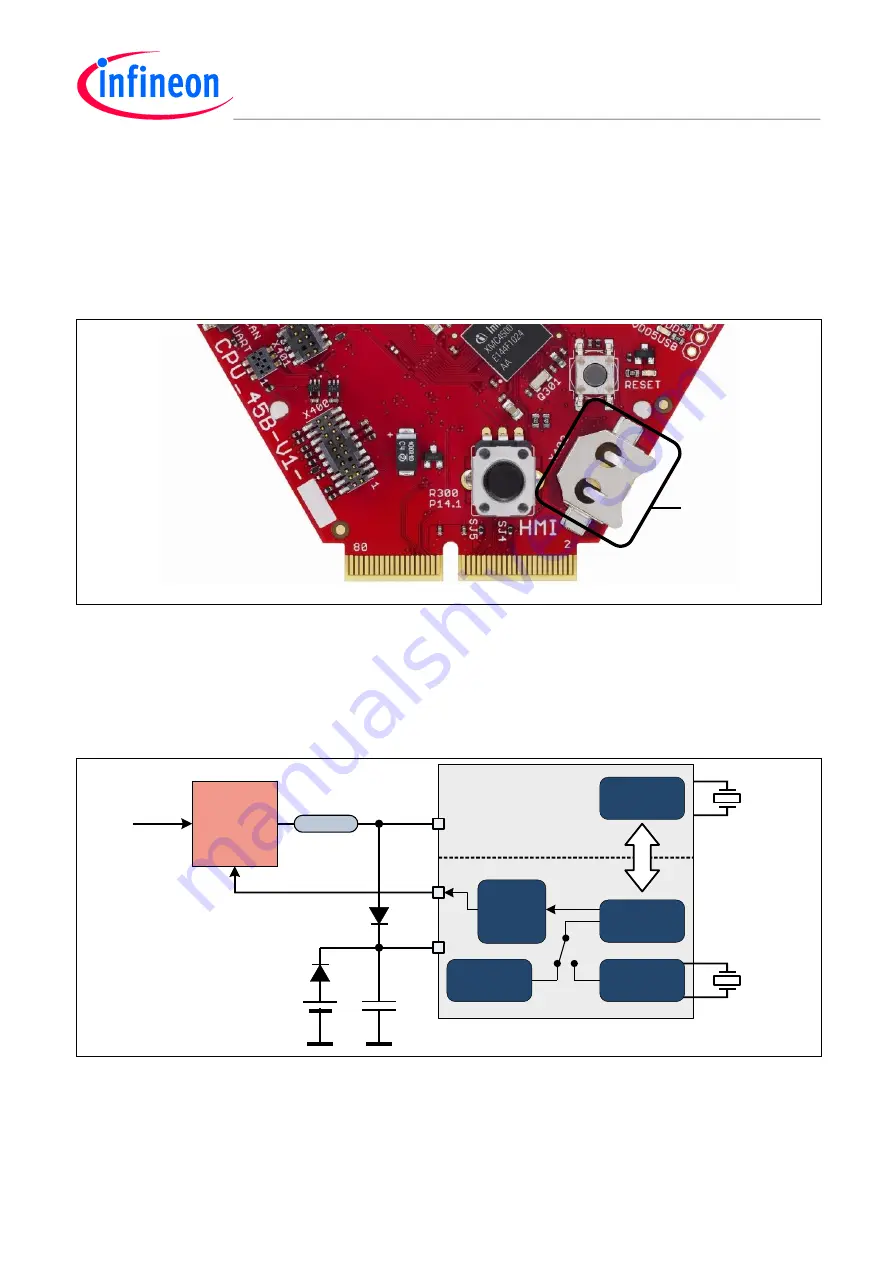

Figure 20

XMC4500 Power Domains and Real Time Clock

Batt.emf

Battery

Holder

Core Domain

CPU

Internal OSC

Hibernate Domain

VBAT

32.768 kHz

XMC4500

VDDP

IFX1763

LDO

Voltage Reg.

VDD3.3

+

RTC

S

P

I

RTC.emf

Battery

12 MHz

External OSC

Hibernate

Control

HIBIO_1

EN