CPU_45B-V1

CPU Board XMC4500 SDRAM

Hardware Description

Board User's Manual

25

Revision 1.0, 2013-02-20

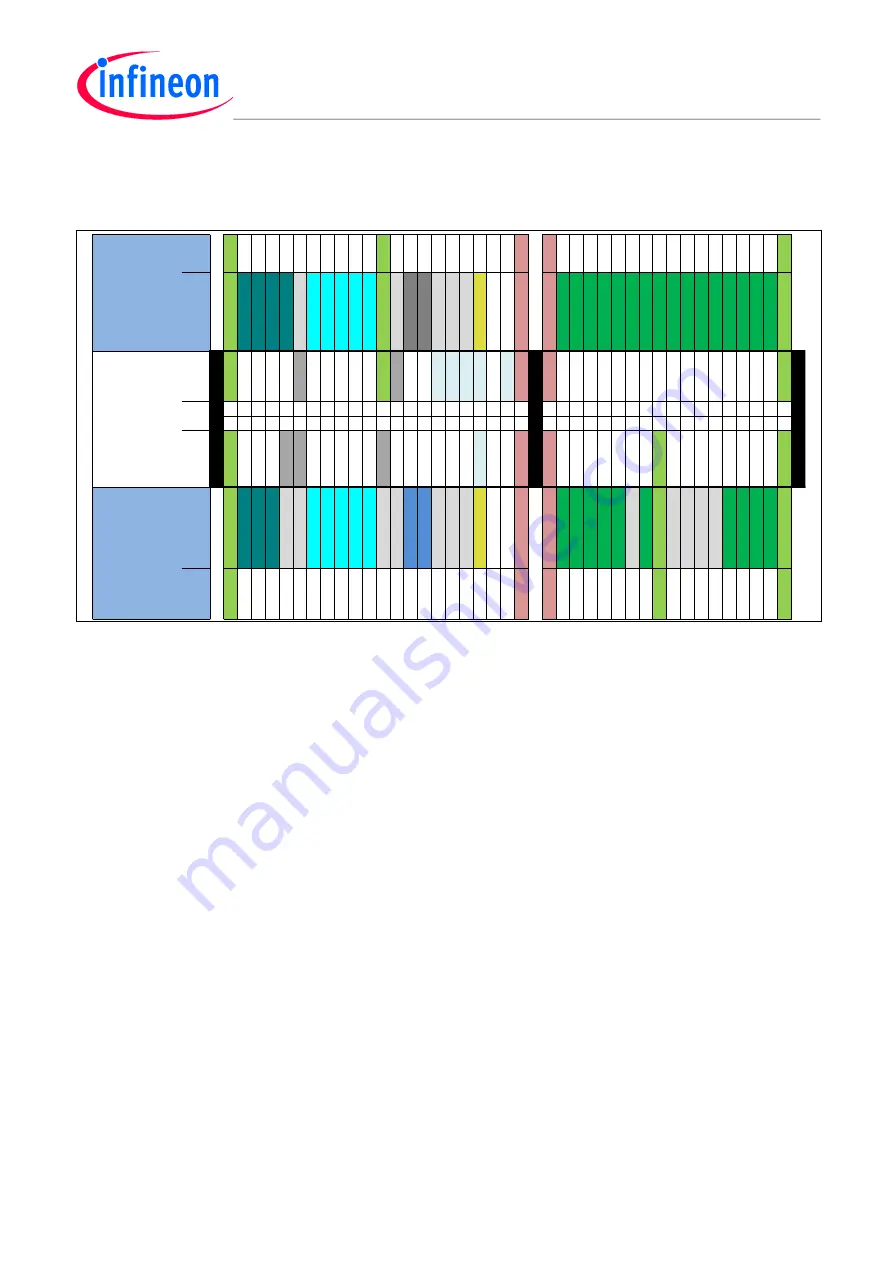

2.12.1

COM Connector

The COM satellite connector on the CPU_45B-V1 board allows interface expansion through COM satellite cards

(e.g. COM_ETH-V1)

XM

C P

in

VSS

P

3

.15

P

3

.14

P

0

.15

P

0

.14

nc

P

2

.13

P

2

.12

P

1

5

.9

P

0

.11

P

1

5

.8

VSS

nc

P

2

.7

P

2

.6

nc

nc

nc

P

3

.13

P

6

.3

P

ORST

P

0

.2

P

0

.3

P

0

.4

P

0

.5

P

3

.5

P

3

.6

P

0

.7

P

0

.8

P

4

.0

P

4

.1

P

1

.6

P

1

.7

P

1

.8

P

1

.9

P

1

.2

P

1

.3

VSS

XM

C Fu

n

ctio

n

GN

D

U1

C1

_D

OUT0

U1

C1

_D

OUT1

U1

C1

_D

OUT2

U1

C1

_D

OUT3

nc

ET

H

0

_T

XD

1

ET

H

0

_T

XD

0

ET

H

0

_CRS_D

VC

ET

H

0

_RX

ERB

ET

H

0

_CL

K_

RM

II

C

GN

D

nc

CA

N

_N1_

TX

D

CA

N

_N1_

RX

D

A

nc

nc

nc

U2

C1

_SCL

KOUT

P

6

.3

RESET#

EBU_AD

0

EBU_AD

1

EBU_AD

2

EBU_AD

3

EBU_AD

4

EBU_AD

5

EBU_AD

6

EBU_AD

7

EBU_AD

8

EBU_AD

9

EBU_AD

1

0

EBU_AD

1

1

EBU_AD

1

2

EBU_AD

1

3

EBU_AD

1

4

EBU_AD

1

5

GN

D

Fu

n

ctio

n

GN

D

q

SPI_D

0

q

SPI_D

1

q

SPI_D

2

q

SPI_D

3

RSV

D

ET

H

_RM

II

ET

H

_RM

II

ET

H

_RM

II

ET

H

_RM

II

ET

H

_RM

II

GN

D

RSV

D

CA

N

_T

XD

CA

N

_RX

D

SPI_M

TSR

SPI_M

RST

SPI_SCL

K

I2C_

SCL

GP

IO

RESET

VDD

5

VDD

5

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

EBU_AD

GN

D

Satellite

2

4

6

8 10 12 14 16 18 20 22 24 26 28 30 32 34 36 38 40 42 44

46 48 50 52 54 56 58 60 62 64 66 68 70 72 74 76 78 80

Connector

1

3

5

7

9 11 13 15 17 19 21 23 25 27 29 31 33 35 37 39 41 43

45 47 49 51 53 55 57 59 61 63 65 67 69 71 73 75 77 79

Fu

n

ctio

n

GN

D

q

SPI_SCL

K

q

SPI_CS

q

SPI_CS

RSV

D

RSV

D

ET

H

_RM

II

ET

H

_RM

II

ET

H

_RM

II

ET

H

_RM

II

ET

H

_RM

II

RSV

D

AS

C_D

IR

AS

C_RX

D

AS

C_T

XD

SPI_CSC0

SPI_CSC1

SPI_CSC2

I2C_

SDA

COM

_GP

IO1

COM

_GP

IO0

VDD

5

VDD

5

EBU_AD

V

EBU_W

R

EBU_RD

EBU_BC

EBU_BC

EBU_CS

EBU_CS

GN

D

EBU_A

EBU_A

EBU_A

EBU_A

EBU_A

EBU_A

EBU_A

EBU_A

GN

D

XM

C Fu

n

ctio

n

GN

D

U1

C1

_SCL

KOUT

U1

C1

_SEL

O0

U1

C1

_SEL

O1

nc

nc

ET

H

0

_RX

D

1

D

ET

H

0

_RX

D

0

D

ET

H

0

_M

D

O

ET

H

0

_M

D

C

ET

H

0

_T

X_

EN

nc

nc

U0

C0

_D

X0

B

U0

C0

_D

OUT0

nc

nc

nc

U2

C1

_D

OUT0

/D

X0

D

P

1

4

.13

P

0

.0

EBU.n

ADV

EBU_RD

/EBU_nWR

EBU_RD

EBU_nBC1

EBU_nBC0

nc

EBU_nCS

1

GN

D

nc

nc

nc

nc

EBU_A19

EBU_A18

EBU_A17

EBU_A16

GN

D

XM

C P

in

VSS

P

0

.13

P

0

.12

P

3

.3

*

nc

nc

P

5

.1

P

5

.0

P

1

.11

P

1

.10

P

5

.9

nc

nc

P

1

.4

**

P

1

.5

**

nc

nc

nc

P

3

.11

/P

3

.12

P

1

4

.13

P

0

.0

P

0

.6

P

3

.1

P

3

.0

P

2

.15

P

2

.14

nc

P

0

.9

VSS

nc

nc

nc

nc

P

6

.4

P

6

.2

P

6

.1

P

6

.0

VSS

C

OM

CPU_45B-V1

(SDRAM)

CPU_45B-V1

(SDRAM)

P

in

C

OM

C

OM

Figure 23

Satellite Connector Type COM

Attention: * This pin is used as chip select signal for the on-board EEPROM and therefore disconnected

by solder jumper SJ1

Attention: ** This pin is connected with the satellite connector via an analog switch