CY8CKIT-064S0S2-4343W PSoC 64 Standard Secure – AWS Wi-Fi BT Pioneer Kit Guide, Doc. # 002-30680 Rev. *B

44

Hardware

4.2.11

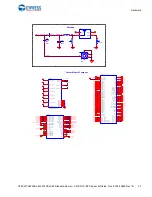

Cypress Quad SPI F-RAM

The PSoC 64 Standard Secure – AWS Wi-Fi BT Pioneer Board contains a CY15B104QSN

Excelon™ F-RAM device, which can be accessed through Quad SPI interface. The F-RAM is 4-Mbit

(512K × 8) and is capable of Quad SPI speed up to 108 MHz but the PSoC 64 MCU is limited to 80

MHz.

Figure 4-15. Schematics of Quad SPI F-RAM

4.2.12

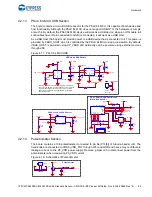

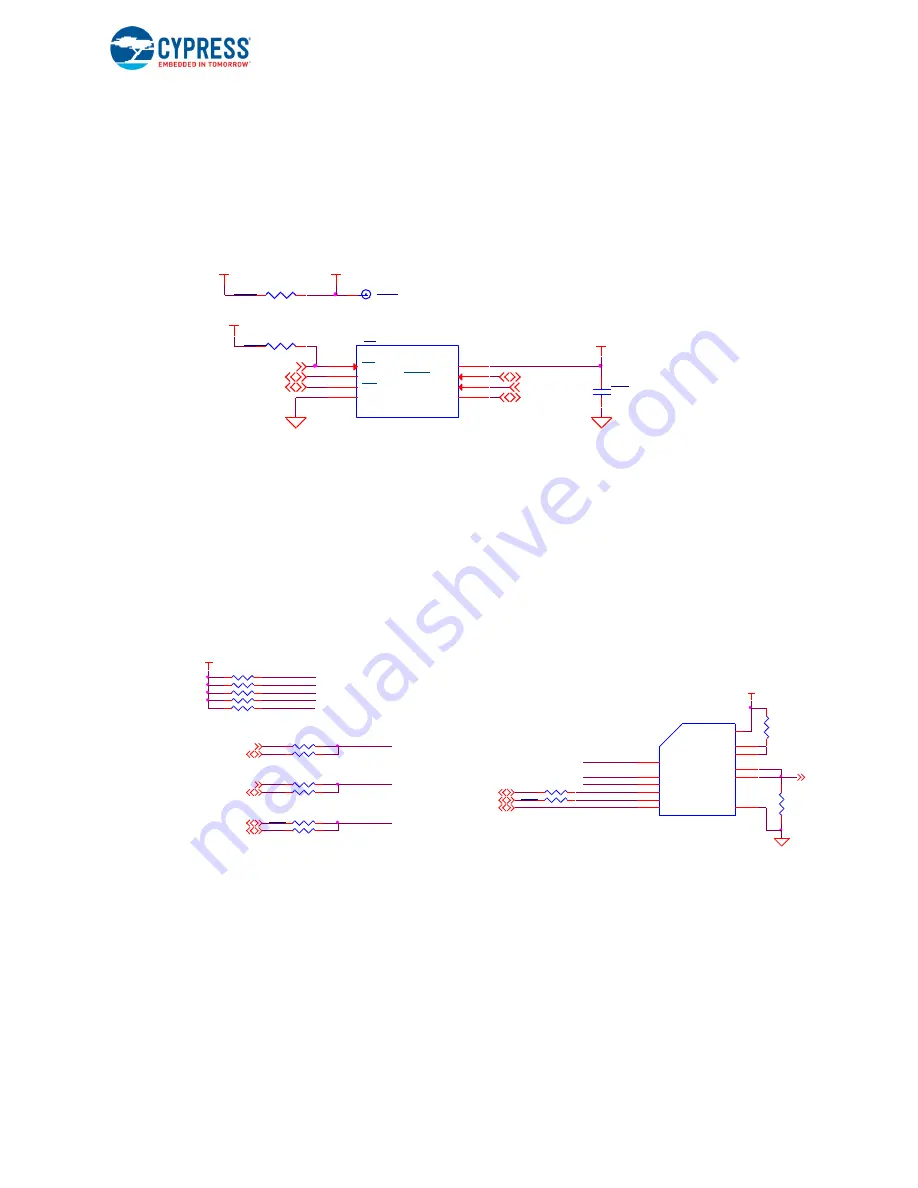

microSD card section

The PSoC 64 Standard Secure – AWS Wi-Fi BT Pioneer Board contains a bottom-mounted microSD

card holder with card detect pin that is connected to the PSoC 64 MCU. It is powered by VDD_VD-

DIO0 (connected to VCC_3V3 by default). The PSoC 64 MCU is capable of UHS-I but is limited to

High-Speed mode (50 MHz clock) in this kit.

By default, the PSoC 64 MCU device is connected using an SDHC interface but optionally can be

connected using SPI by re-working a few zero-ohm resistors.

Figure 4-16. Schematics of microSD Card Section

U4

CY 15B104QSN

CS

1

SO/IO1

2

WP/IO2

3

VSS

4

SI/IO0

5

SCK

6

RESET/IO3

7

VDD

8

Quad SPI F-RAM

FRAM_VDD

FRAM_VDD

FRAM_SS_L

VCC_VDDIO0

FRAM_VDD

C69

0.1uF

16V

QSPI_SCK

QSPI_IO0

QSPI_IO1

QSPI_IO2

QSPI_IO3

R113

10K

R109

0 OHM

TP10

R34

49.9K

J20

MICROSD CARD SOCKET

DAT2

1

DAT3

2

CMD

3

VDD

4

CLK

5

VSS

6

DAT0

7

DAT1

8

CD1

9A

CD_COM1

10A

CD_COM2

10B

CD2

9B

R46

4.7K

SD_CD_L

VCC_VDDIO0

J_SD_DAT2

J_SD_DAT3

J_SD_CLK

J_SD_DAT0

J_SD_DAT1

J_SD_CMD

R169

0 OHM

No Load

R168

0 OHM

R167

0 OHM

No Load

R166

0 OHM

R164

0 OHM

R165

0 OHM

No Load

J_SD_CMD

J_SD_CLK

J_SD_DAT0

R163

0 OHM

R162

0 OHM

SD_DAT0

SD_DAT2

SD_DAT1

J_SD_DAT0

J_SD_DAT1

J_SD_DAT2

J_SD_DAT3

J_SD_CMD

R43

49.9K

R40

49.9K

R42

49.9K

R39

49.9K

R41

49.9K

SD_DAT3

VDDIO0

SD_CLK

SD_DAT0

SD_DAT1

SD_DAT2

microSD Card Section

SD_CMD

Note: Load R165, R167 and R169 and

remove R162, R163, R164, R166 and R168

to change from SDHC to SPI interface to

microSD card