Data Sheet

131

Rev. 1.00

2017-07-31

TLE9262BQXV33

Serial Peripheral Interface

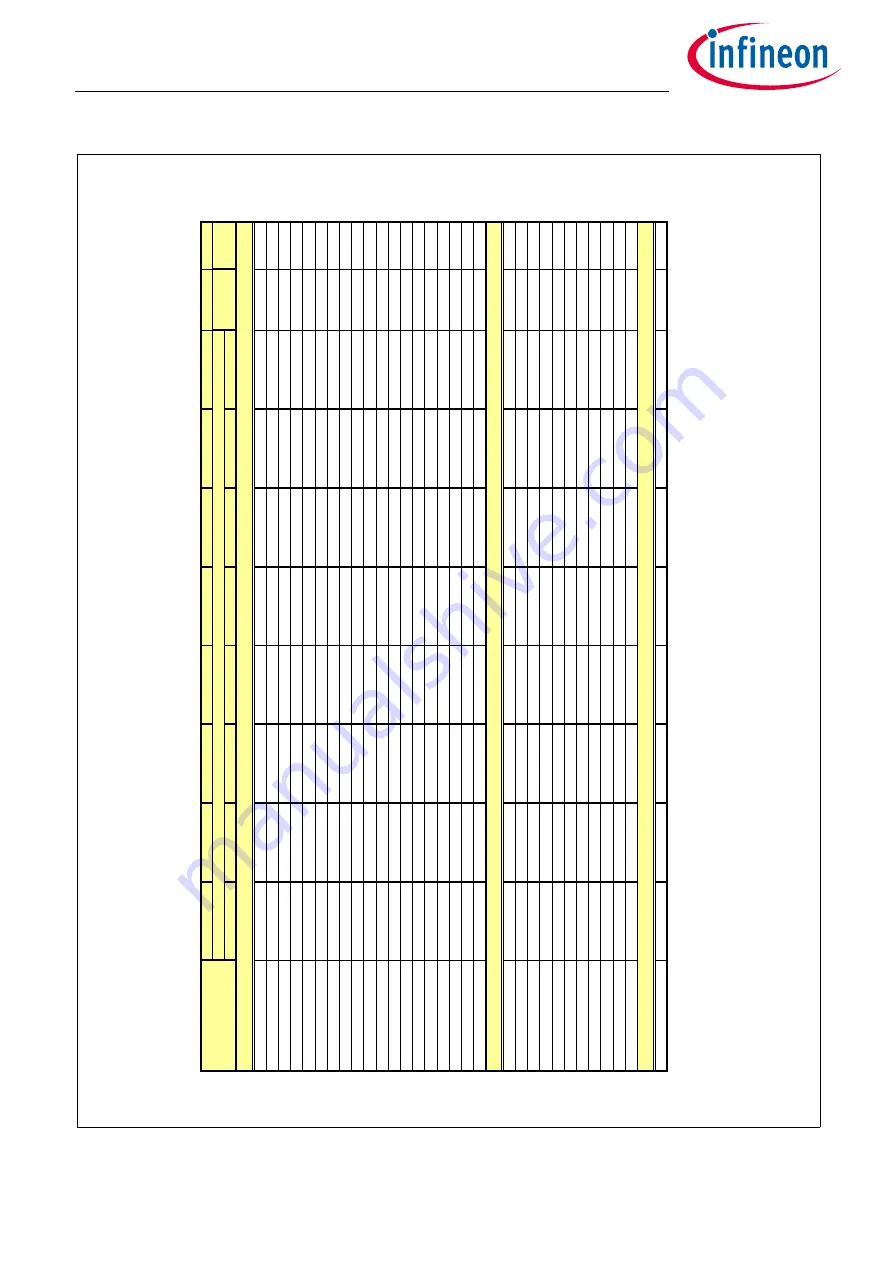

Figure 57 TLE9262BQXV33 SPI Bit Mapping

15

14

13

12

11

10

9

8

7

6...0

Data Bit 15…8

D7

D6

D5

D4

D3

D2

D1

D0

M

_

S

_CT

RL

MODE_1

MODE_0

VCC3_ON

V

CC2_ON_1

VCC2_ON_0

V

CC1_OV_RST

V

CC1_RT

_1

VCC1_RT

_0

read/w

rite

0000001

HW

_CT

RL

VCC3_V

_CFG

SOFT

_RESET

_RO

FO_ON

VCC3_VS_UV_OFF

VCC3_LS

reserved

VCC

3_LS_ST

P

_O

N

CFG

read/w

rite

0000010

W

D_CT

RL

CHECK

SUM

W

D_ST

M

_EN_0

W

D_W

IN

W

D_EN_W

K_B

U

S

reserved

W

D_T

IME

R_2

W

D_T

IME

R_1

W

D_T

IME

R_0

read/w

rite

0000011

BUS_CT

RL_1

LIN_FLA

S

H

LIN_LS

M

LIN_T

X

D_T

O

LIN1_1

LIN1_0

reserved

CAN_1

CAN_0

read/w

rite

0000100

BUS_CT

RL_2

reserved

reserved

I_PEAK_T

H

reserved

reserved

reserved

reserved

reserved

read/w

rite

0000101

W

K_CT

RL_1

T

IME

R2_W

K_E

N

T

IME

R1_W

K_E

N

reserved

reserved

reserved

W

D_ST

M

_EN_1

reserved

reserved

read/w

rite

0000110

W

K_CT

RL_2

INT

_GLOBAL

reserved

W

K

_MEAS

reserved

reserved

W

K

3_EN

W

K

2_EN

W

K

1_EN

read/w

rite

0000111

W

K_PUPD_CT

RL

reserved

reserved

W

K

3_PUPD_1

W

K

3_PUPD_0

W

K

2_PUPD_1

W

K

2_PUPD_0

W

K

1_PUPD_1

W

K

1_PUPD_0

read/w

rite

0001000

W

K_FLT

_CT

RL

reserved

reserved

W

K

3_FLT

_

1

W

K3_FLT

_0

W

K

2_FLT

_

1

W

K2_FLT

_0

W

K

1_FLT

_

1

W

K1_FLT

_0

read/w

rite

0001001

T

IM

E

R1_CT

RL

reserved

T

IME

R1_ON_2

T

IME

R1_ON_1

T

IME

R1_ON_0

reserved

T

IME

R1_P

ER_2

T

IME

R1_P

ER_1

T

IME

R1_P

ER_0

read/w

rite

0001100

T

IM

E

R2_CT

RL

reserved

T

IME

R2_ON_2

T

IME

R2_ON_1

T

IME

R2_ON_0

reserved

T

IME

R2_P

ER_2

T

IME

R2_P

ER_1

T

IME

R2_P

ER_0

read/w

rite

0001101

SW

_S

D_CT

RL

reserved

HS_OV_S

D_EN

H

S_UV

_S

D_EN

H

S_OV_UV_REC

reserved

reserved

reserved

reserved

read/w

rite

0010000

HS_CT

RL_1

reserved

HS2_2

H

S2_1

HS2_0

reserved

HS1_2

H

S1_1

HS1_0

read/w

rite

0010100

HS_CT

RL_2

reserved

HS4_2

H

S4_1

HS4_0

reserved

HS3_2

H

S3_1

HS3_0

read/w

rite

0010101

GPIO_CT

RL

FO_DC_1

FO_DC_0

GPIO2_2

G

PIO2_1

GPIO2_0

G

PI

O1_2

GPIO1_1

G

PIO1_0

read/w

rite

0010111

PW

M

1

_CT

R

L

PW

M1_DC_7

PW

M1_DC_6

PW

M1_DC_5

PW

M1_DC_4

PW

M1_DC_3

PW

M1_DC_2

PW

M1_DC_1

PW

M1_DC_0

read/w

rite

0011000

PW

M

2

_CT

R

L

PW

M2_DC_7

PW

M2_DC_6

PW

M2_DC_5

PW

M2_DC_4

PW

M2_DC_3

PW

M2_DC_2

PW

M2_DC_1

PW

M2_DC_0

read/w

rite

0011001

PW

M

_FREQ_CT

RL

reserved

reserved

reserved

reserved

reserved

PW

M2_FREQ_0

reserved

PW

M1_FREQ_0

read/w

rite

0011100

SY

S_S

T

A

T

_CT

RL

SY

S_ST

AT

_7

SY

S_ST

AT

_6

SY

S_ST

AT

_5

SY

S_ST

AT

_4

SY

S_ST

AT

_3

SY

S_ST

AT

_2

SY

S_ST

AT

_1

SY

S_ST

AT

_0

read/w

rite

0011110

SUP_ST

A

T

_2

reserved

VS_UV

reserved

VCC3_OC

V

CC3_UV

VCC3_OT

V

CC1_OV

V

CC1_W

ARN

read/clear

1000000

SUP_ST

A

T

_1

POR

VSHS_UV

VSHS_OV

VCC2_OT

V

CC2_UV

VCC1_S

C

V

CC1_UV_FS

VCC1_UV

read/clear

1000001

TH

E

R

M

_

S

T

A

T

reserved

reserved

reserved

reserved

reserved

T

S

D2

T

S

D1

T

P

W

read/clear

1000010

DEV_S

T

A

T

DEV_ST

AT

_1

DEV_ST

AT

_0

reserved

reserved

W

D_FAIL_1

W

D_FAIL_0

SPI_FAIL

FAILURE

read/clear

1000011

BUS_ST

A

T

_1

reserved

LIN1_FAIL_1

LIN1_FAIL_0

reserved

reserved

CAN_FAIL_1

CAN_FAIL_0

VCAN_UV

read/clear

1000100

BUS_ST

A

T

_2

reserved

reserved

reserved

reserved

reserved

reserved

reserved

reserved

read/clear

1000101

W

K

_

S

TA

T_

1

reserved

LIN1_W

U

C

AN_W

U

T

IME

R_W

U

reserved

W

K

3_W

U

W

K

2_W

U

W

K

1_W

U

read/clear

1000110

W

K

_

S

TA

T_

2

reserved

reserved

GPIO2_W

U

GPIO1_W

U

reserved

reserved

reserved

reserved

read/clear

1000111

W

K_LVL_ST

A

T

SBC_DEV_LVL

CF

G

P

G

P

IO

2_LVL

G

PIO

1

_LVL

reserved

W

K

3_LVL

W

K2_LVL

W

K

1_LVL

read

1001000

HS_OC_OT

_

S

T

A

T

reserved

reserved

reserved

reserved

HS4_O

C_OT

H

S3_O

C_OT

H

S2_O

C_OT

H

S1_O

C_OT

read/clear

1010100

HS_OL_S

T

A

T

reserved

reserved

HS4_O

L

HS3_O

L

HS2_O

L

HS1_O

L

read/clear

1010101

FA

M

_

P

R

OD_ST

A

T

FAM_3

F

AM_2

FAM_1

F

AM_0

PRO

D_3

PRO

D_2

PRO

D_1

PRO

D_0

read

1111110

F A

M

I LY

A

N D P

R O D U C T

R E G I S

T

E R S

Register Short Name

A

c

cess

M

ode

A

ddress

A

6…A

0

C O

N T

R O

L R E G

I

S T

E R S

S T

A

T

U S R E

G I S

T

E R S