Data Sheet

139

Rev. 1.00

2017-07-31

TLE9262BQXV33

Serial Peripheral Interface

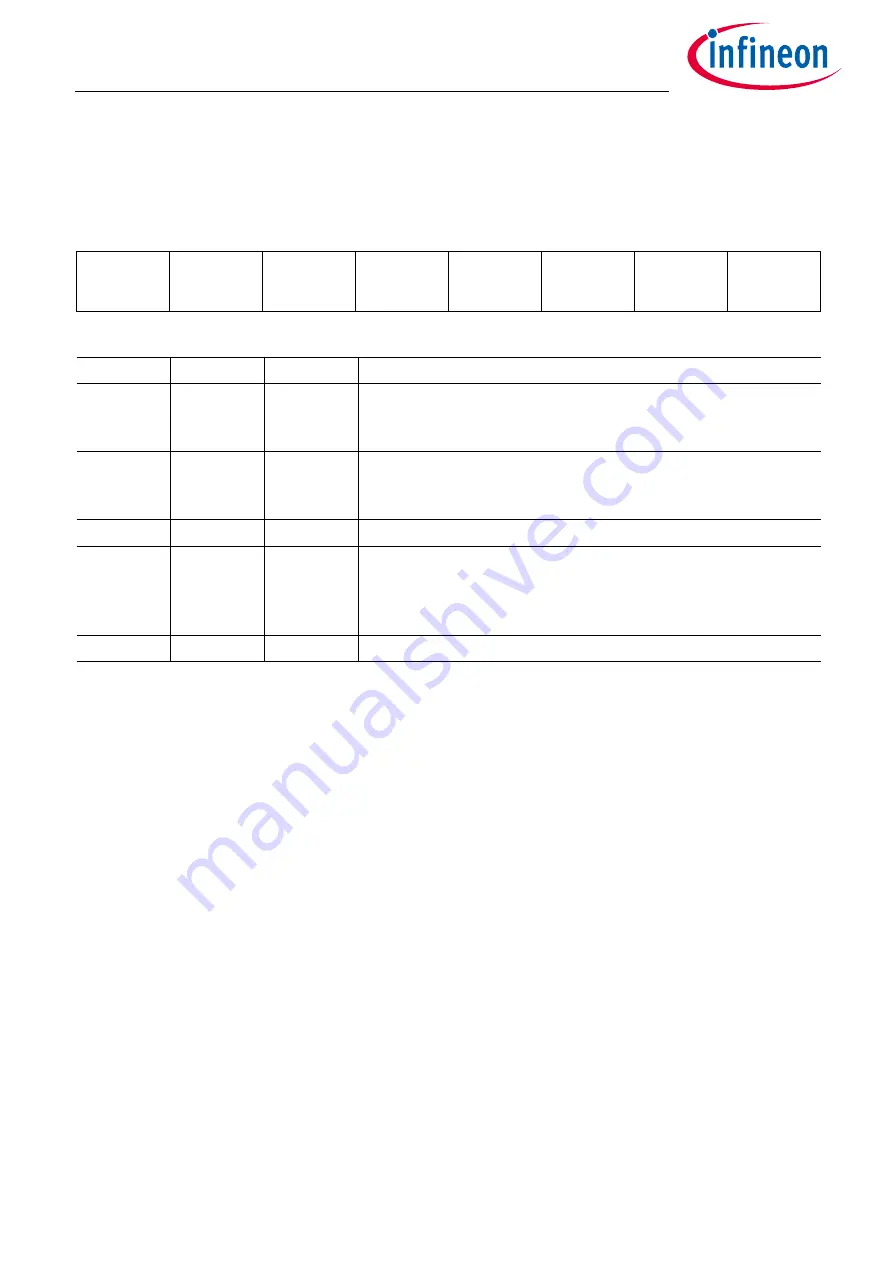

WK_CTRL_1

Internal Wake Input Control (Address 000 0110

B

)

POR / Soft Reset Value: 0000 0000

B

; Restart

Value:

xx00 0000

B

7

6

5

4

3

2

1

0

TIMER2_WK_

EN

TIMER1_WK_

EN

Reserved

Reserved

Reserved

WD_STM_

EN_1

Reserved

Reserved

r

rw

rw

r

r

r

rwh

r

r

Field

Bits

Type

Description

TIMER2_WK

_EN

7

rw

Timer2 Wake Source Control (for cyclic wake)

0B , Timer2 wake disabled

1B , Timer2 is enabled as a wake source

TIMER1_WK

_EN

6

rw

Timer1 Wake Source Control (for cyclic wake)

0B , Timer1 wake disabled

1B , Timer1 is enabled as a wake source

Reserved

5:3

r

Reserved, always reads as 0

WD_STM_

EN_1

2

rwh

Watchdog Deactivation during Stop Mode, bit 1

(

Chapter 15.2.4

)

0B , Watchdog is active in Stop Mode

1B , Watchdog is deactivated in Stop Mode

Reserved

1:0

r

Reserved, always reads as 0