Data Sheet

159

Rev. 1.00

2017-07-31

TLE9262BQXV33

Serial Peripheral Interface

Note:

GPIOx_LVL is updated in SBC Normal and Stop Mode if configured as wake input, low-side switch or

high-side switch.

In cyclic sense or wake mode, the registers contain the sampled level, i.e. the registers are updated

after every sampling. The GPIOs are not capable of cyclic sensing.

If selected as GPIO then the respective level is shown even if configured as low-side or high-side.

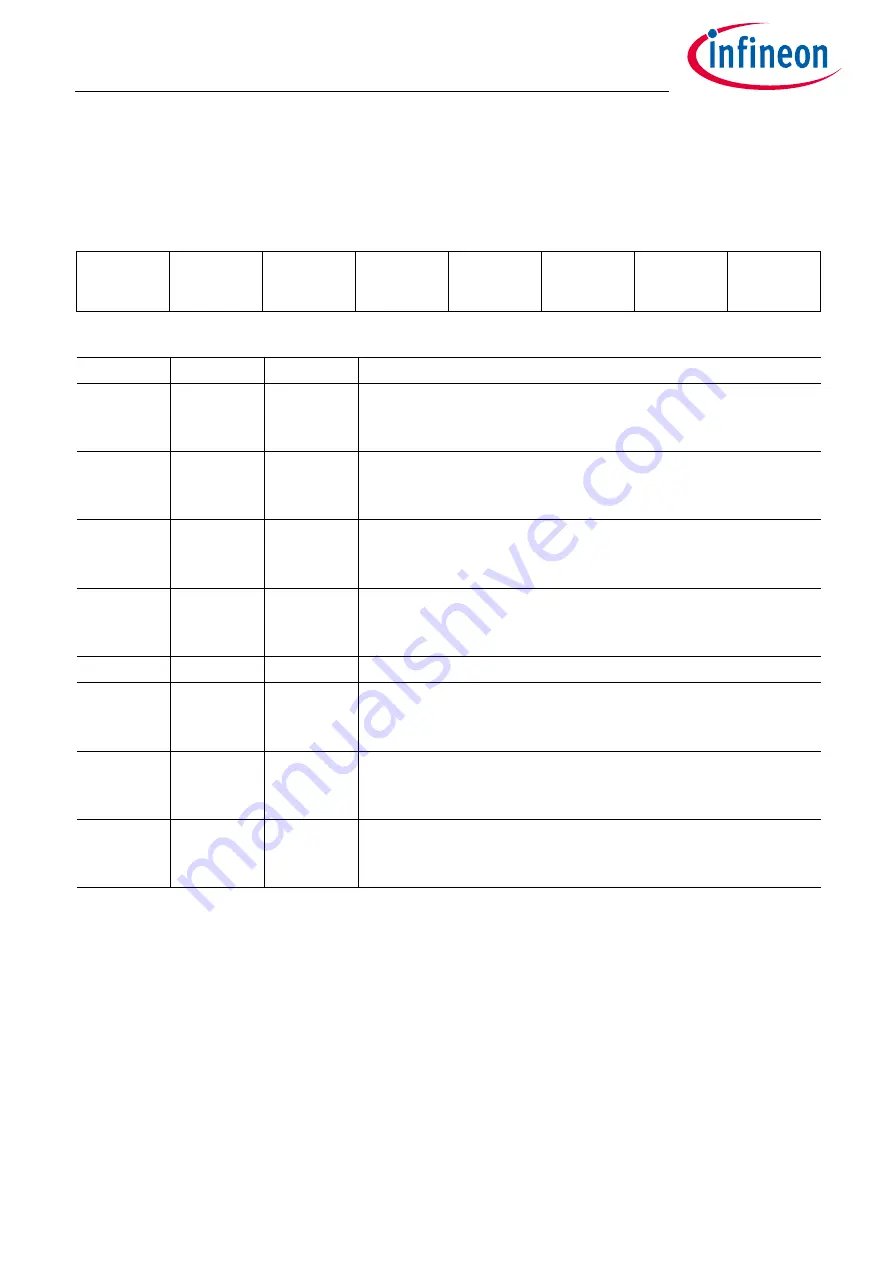

WK_LVL_STAT

WK Input Level (Address 100 1000

B

)

POR / Soft Reset Value: xx00 0xxx

B

;

Restart Value: xxxx 0xxx

B

7

6

5

4

3

2

1

0

SBC_DEV

_LVL

CFGP

GPIO2_LVL

GPIO1_LVL

Reserved

WK3_LVL

WK2_LVL

WK1_LVL

r

r

r

r

r

r

r

r

r

Field

Bits

Type

Description

SBC_DEV

_LVL

7

r

Status of SBC Operating Mode at FO3/TEST Pin

0B , User Mode activated

1B , SBC Development Mode activated

CFGP

6

r

Device Configuration Status

0B , No external pull-up resistor connected on INT (Config 2/4)

1B , External pull-up resistor connected on INT (Config 1/3)

GPIO2_LVL

5

r

Status of GPIO2 (if selected as GPIO)

0B , Low Level (=0)

1B , High Level (=1)

GPIO1_LVL

4

r

Status of GPIO1 (if selected as GPIO)

0B , Low Level (=0)

1B , High Level (=1)

Reserved

3

r

Reserved, always reads as 0

WK3_LVL

2

r

Status of WK3

0B , Low Level (=0)

1B , High Level (=1)

WK2_LVL

1

r

Status of WK2

0B , Low Level (=0)

1B , High Level (=1)

WK1_LVL

0

r

Status of WK1

0B , Low Level (=0)

1B , High Level (=1)