Data Sheet

30

Rev. 1.00

2017-07-31

TLE9262BQXV33

System Features

5.1.5

SBC Restart Mode

There are multiple reasons to enter the SBC Restart Mode. The purpose of the SBC Restart Mode is to reset the

microcontroller:

•

in case of undervoltage on VCC1 in SBC Normal and in SBC Stop Mode,

•

in case of overvoltage on VCC1 if the bit

VCC1_OV_RST

is set and if

CFGP

= ‘1’,

•

due to 1st incorrect Watchdog triggering (only if Config1, Config3 or Config 4 is selected, otherwise SBC Fail-

Safe Mode is immediately entered),

•

In case of a wake event from SBC Sleep or SBC Fail-Safe Mode or a release of overtemperature shutdown

(TSD2) out of SBC Fail-Safe Mode this transition is used to ramp up VCC1 after a wake in a defined way.

From SBC Restart Mode, the SBC goes automatically to SBC Normal Mode, i.e the mode is left automatically

by the SBC without any microcontroller influence. The SBC

MODE

bits are cleared. As shown in

Figure 47

the

Reset Output (RO) is pulled low when entering Restart Mode and is released at the transition to Normal Mode

after the reset delay time (

t

RD1

). The watchdog timer will start with a long open window starting from the

moment of the rising edge of RO and the watchdog period setting in the register

WD_CTRL

will be changed to

the respective default value ‘100’.

Leaving the SBC Restart Mode will not result in changing / deactivating the Fail outputs.

The behavior of the blocks is listed below:

•

All FOx outputs are activated in case of a 1st watchdog trigger failure (if Config1 or Config2 is selected) or

in case of VCC1 overvoltage detection (if

VCC1_OV_RST

is set)

•

VCC1 is ON or ramping up

•

VCC2 will be disabled if it was activated before

•

VCC3 is fixed or ramping as configured in SBC Normal Mode

• CAN is “woken” due to a wake event or OFF depending on previous SBC and transceiver mode (see also

Chapter 10

). It is wake capable when it was in CAN Normal-, Receive Only or wake capable mode before

SBC Restart Mode

•

LIN is “woken” or OFF depending on previous SBC and transceiver mode (see also

Chapter 11

). It is wake

capable when it was in LIN Normal-, Receive Only or wake capable mode before SBC Restart Mode.

• HS Outputs will be disabled if they were activated before

•

RO is pulled low during SBC Restart Mode

•

SPI communication is ignored by the SBC, i.e. it is not interpreted

• The Restart Mode entry is signalled in the SPI register

DEV_STAT

with the bits

DEV_STAT

Table 7

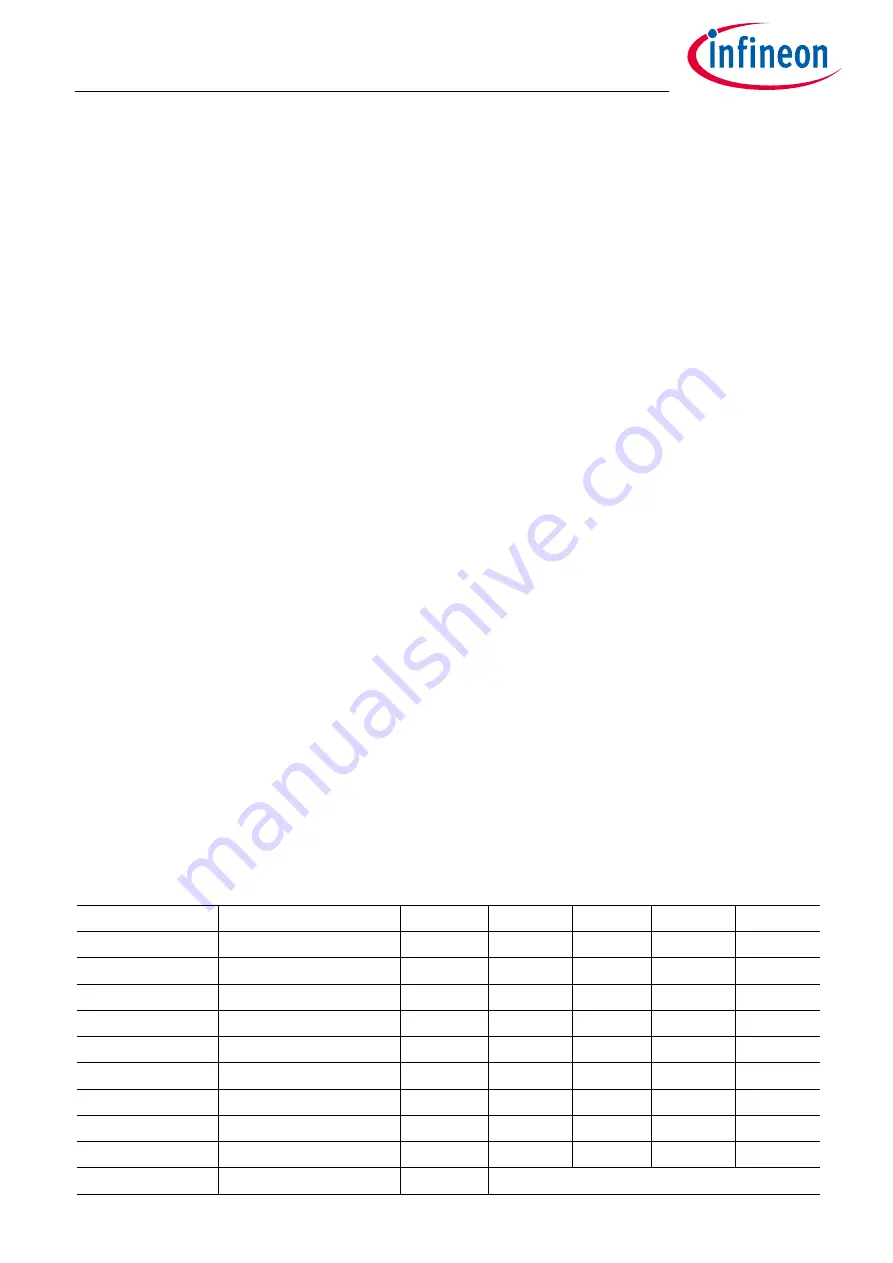

Reasons for Restart - State of SPI Status Bits after Return to Normal Mode

Prev. SBC Mode

Event

DEV_STAT WD_FAIL

VCC1_UV VCC1_OV VCC1_SC

Normal

1x Watchdog Failure

01

01

x

x

x

Normal

2x Watchdog Failure

01

10

x

x

x

Normal

VCC1 undervoltage reset 01

xx

1

x

x

Normal

VCC1 overvoltage reset

01

xx

x

1

x

Stop

1x Watchdog Failure

01

01

x

x

x

Stop

2x Watchdog Failure

01

10

x

x

x

Stop

VCC1 undervoltage reset 01

xx

1

x

x

Stop

VCC1 overvoltage reset

01

xx

x

1

x

Sleep

Wake-up event

10

xx

x

x

x

Fail-Safe

Wake-up event

01

see “Reasons for Fail Safe,

Table 8

”