Data Sheet

38

Rev. 1.00

2017-07-31

TLE9262BQXV33

System Features

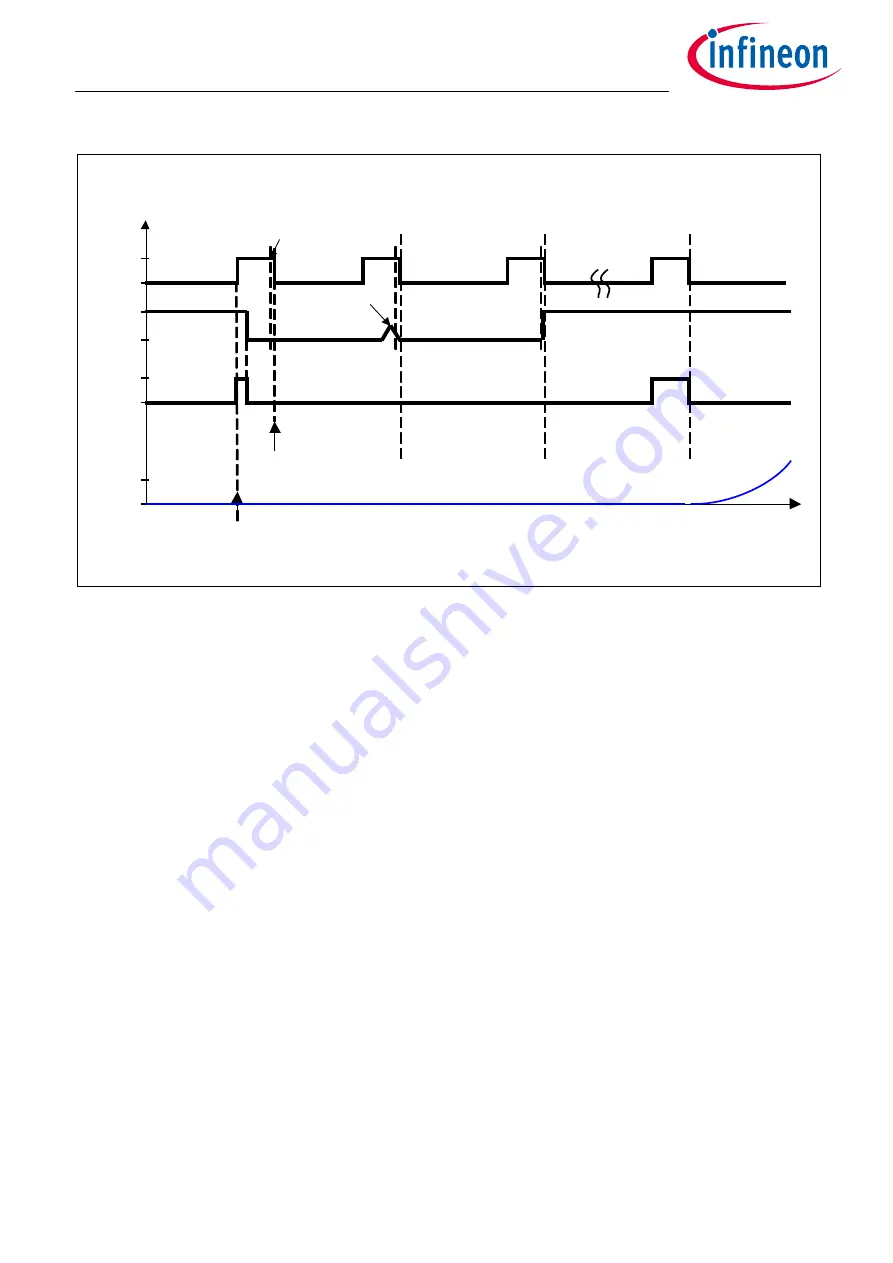

Figure 9

Cyclic Sense Example in SBC Sleep Mode, HSx starts “OFF”/HIGH,

GND based WKx input

The cyclic sense function will not work properly anymore in case of following conditions:

•

in case SBC Fail-Safe Mode is entered: The respective HS Switch will be disabled and the respective wake

pin will be changed to static sensing

•

In SBC Normal, Stop, or Sleep Mode in case of an overcurrent, overtemperature, under- or overvoltage (in

case function is selected) event: the respective HS switch will be disabled

Note:

The internal timers for cyclic sense are not disabled automatically in case the HS switch is turned off

due to above mentioned failures.This must be considered to avoid loss of wake events.

5.2.1.2

Cyclic Sense in Low Power Mode

If cyclic sense is intended for SBC Stop or SBC Sleep Mode mode, it is necessary to activate the cyclic sense in

SBC Normal Mode before going to the low power mode. A wake event due to cyclic sense will set the respective

bit WK1_WU, WK2_WU or WK3_WU. In Stop Mode the wake event will trigger an interrupt, in Sleep Mode the

wake event will send the device via Restart Mode to Normal Mode. Before returning to SBC Sleep Mode, the

wake status register

WK_STAT_1

and

WK_STAT_2

needs to be cleared. Trying to go to SBC Sleep mode with

uncleared wake flags, such as WKx_WU the SBC will directly wake-up from Sleep Mode by going via Restart

Mode to Normal Mode, a reset is issued. The WKx_WU bit is seen as source for the wake. This is implemented

in order not to loose an wake event during the transition.

Start of

Cyclic Sense

High

n-1

Low

open

closed

Filter time

INT &

WK Bit Set

Learning

Cycle

WK

n-1

= Low

WK

n

= Low

WK

n

=

WK

n-1

no wake event

WK

n

= WK

n+1

= Low

(but ignored because

change during filter time )

WK

n

= WK

n+1

no wake event

WK

n+2

= High

WK

n+2

≠

WK

n+1

wake event

n

n+1

n+2

HS

WK

High

Low

Switch

High

Low

VCC1

SBC Sleep Mode

Spike

Transition to:

SBC Normal Mode