© 2019 Infinite Electronics, Inc. Pasternack is a registered trademark of Infinite Electronics, Inc.

21

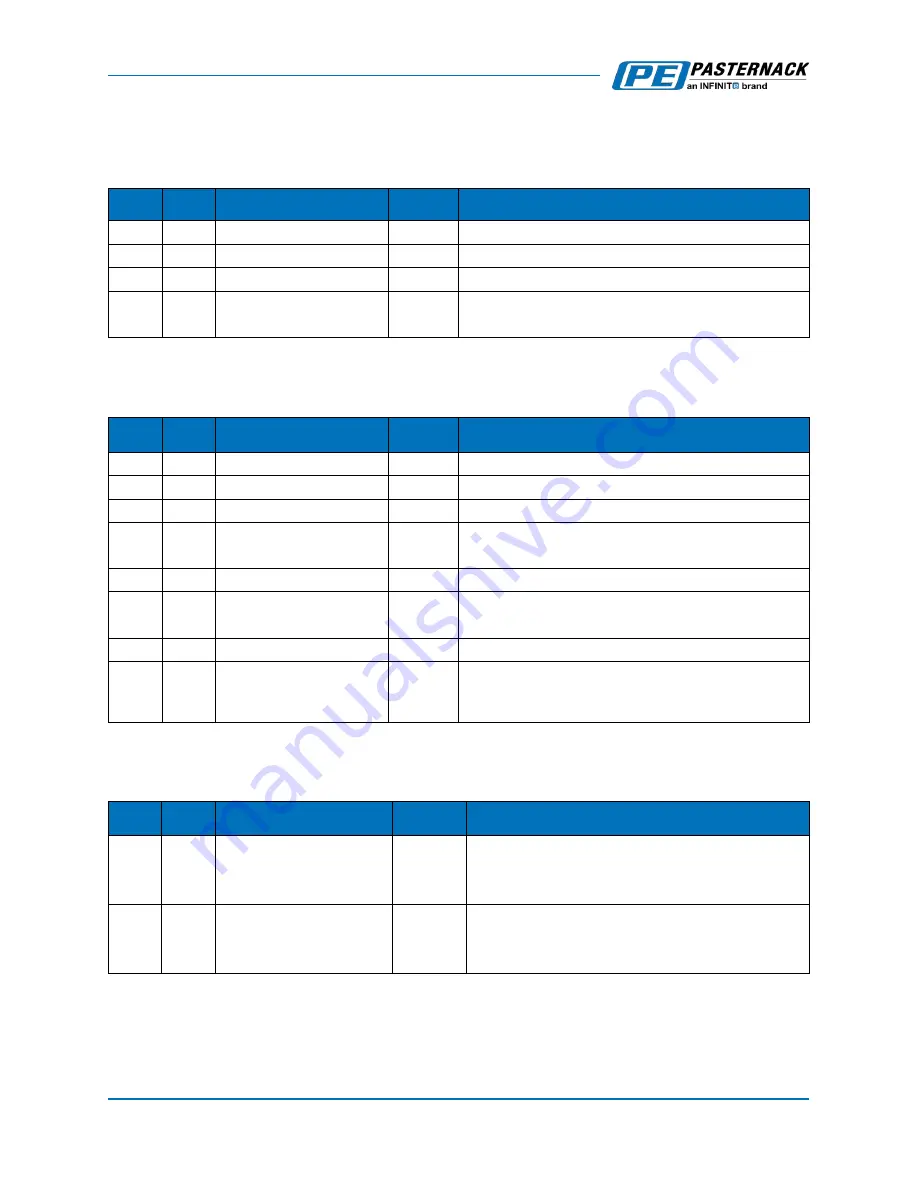

7.2 Reg 00h Strobe (Write Only) Register

Bit

Type

Name

Default

Description

0

STR

global_swrst_regs

0

Strobe to soft reset the SPI registers

1

STR

global_swrst_dig

0

Strobe to soft reset the rest of digital

2

STR

mcnt_resynch

0

Reserved

3

STR

tsens_spi_strobe

0

Strobe to clock the temp measurement on

demand

7.3 Reg 01h Enable & Reset Register

Bit

Type

Name

Default

Description

0

R/W

malg_vcobug_en

1

VCO Buffer Enable

1

R/W

mag_bias_en

1

Bias enable

10:2

R/W

Reserved

479

Reserved

11

R/W

pfd_lkd_en

1

Enable / Resetb to digital lockdetect circuit and

PFD’s lockdetect output gates

12

R/W

cp_en

1

Charge Pump Enable, disable is tri-stated output

13

R/W

dsm_rstb

0

1 - Enables fractional modulator

see also dsm_integer_mode Reg12h<3>

14

R/W

lkd_rstb

1

1 - enables lock detect circuit

15

R/W

pfds_rstb

1

CSP PFD FF rstb

1 - Enables the Cycle Slip Prevention (CSP)

feature of the PFD

7.4 Reg 02h Serial Data Out Force Register

Bit

Type

Name

Default

Description

0

R/W

malg_sdo_driver_force_

val

1

Serial Data Out Force value

This value may be forced onto LD_SDO by

setting malg_sdo_driver_force_en

1

R/W

malg_sdo_driver_force_

en

1

Serial Data Out EN Force enable

Places value from malg_sdo_driver_force_val on

SDO