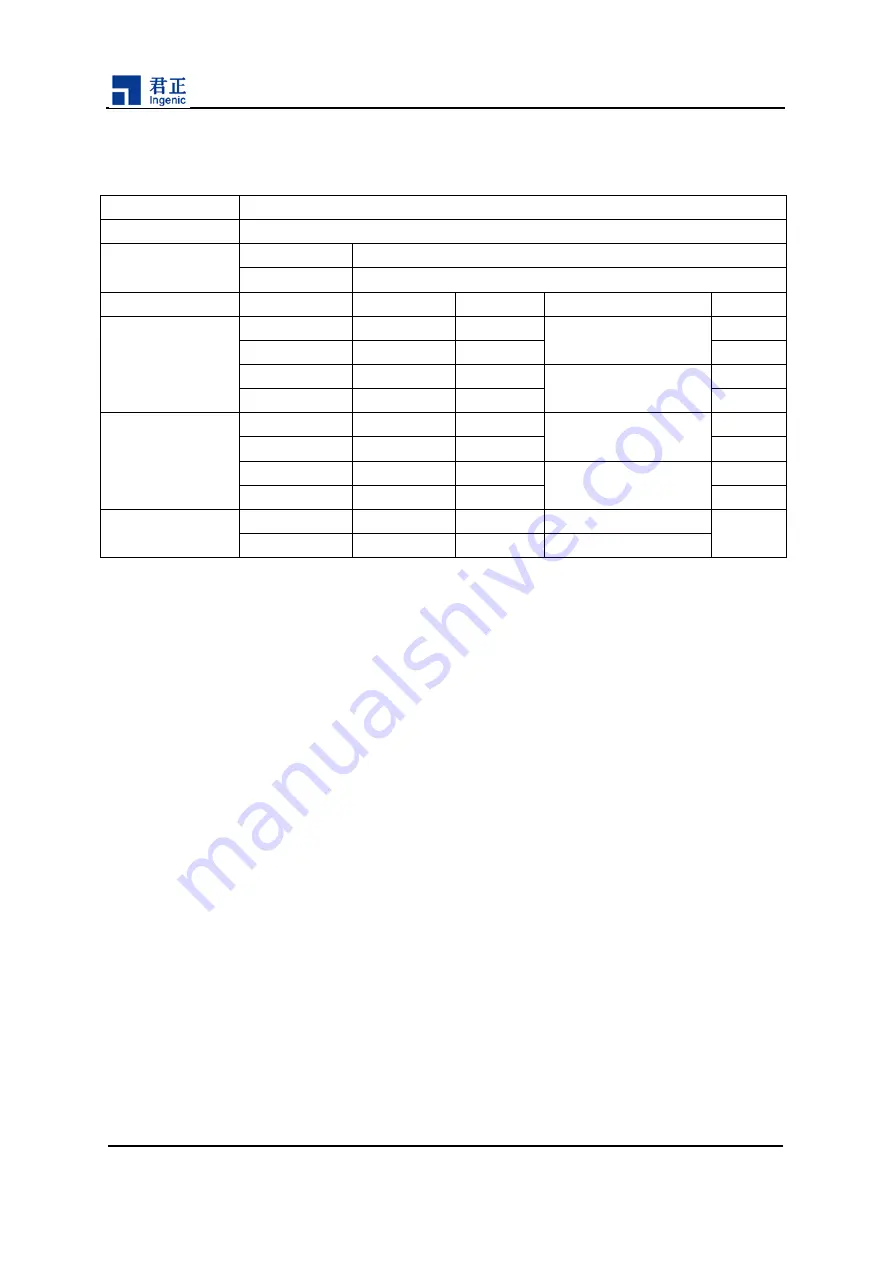

Exceptions and Interrupts

4.2 Exception Vector Locations

Table 4-2 Exception Vector

Exception type

Exception handler entry

reset

0xbfc00000

EJTAG Debug

Prob Trap=0

0xbfc00480

Prob Trap=1

0xff200200

Status.BEV

Status.EXL

Cause.IV

Base

Offset

TLB Refill

0

0

x

EBase[31:12],12'b0

0x000

0

1

x

0x180

1

0

x

0xbfc00200

0x000

1

1

x

0x180

Interrupt

0

x

0

EBase[31:12],12'b0

0x180

0

x

1

0x200+

1

x

0

0xbfc00200

0x180

1

x

1

0x200

Others

0

x

x

EBase[31:12],12'b0

0x180

1

x

x

0xbfc00200

XBurst®2

CPU Core Programming Manual

Copyright © 2005-2020 Ingenic Semiconductor Co., Ltd. All rights reserved.

59