1. Start with the SoC FPGA reference Device Trees provided in the Linux kernel

source code that targets the Intel SoC development kits. They cover the HPS

portion of the device but do not cover the FPGA portion which changes on a per-

project basis. SD/MMC and QSPI versions are provided with the kernel source

code.

2. Edit the Device Tree as necessary to accommodate any board changes as

compared to the Intel SoC development kit.

3. Edit the Device Tree as necessary to accommodate the Linux drivers targeting

FPGA Soft IP.

Note:

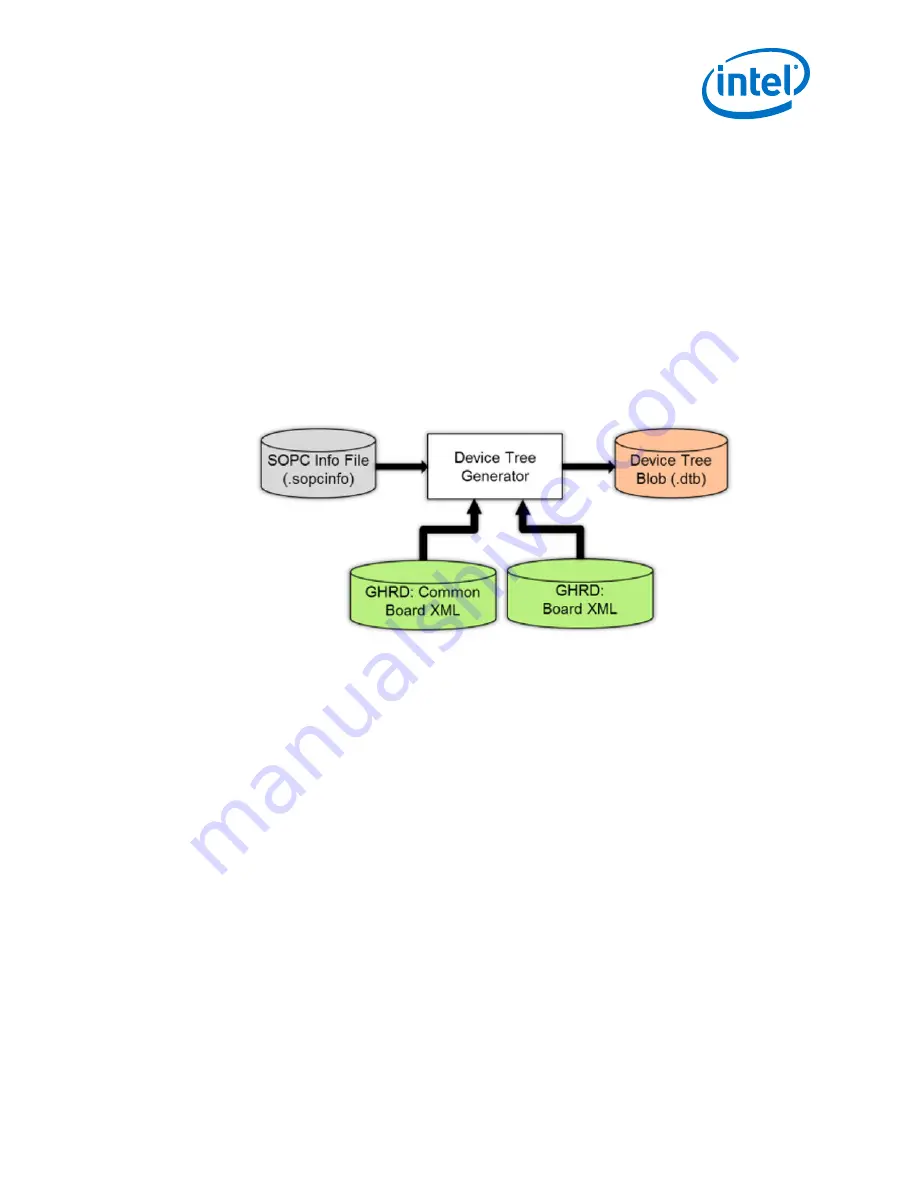

The GSRD for Linux uses a different flow that the one recommended above relying on

a custom tool called “Linux Device Tree Generator” that is provided as part of SoC

EDS.

Figure 11.

Device Tree Generation Flow for GSRD for Linux

Refer to the DeviceTree Generator User Guide link given below for more details

about the Linux Device Tree Generator.

Related Information

DeviceTree Generator User Guide

5.1.4. Assembling a Software Development Platform for a Bare-Metal

Application

Intel hardware libraries (HWLibs) are low level bare metal software libraries provided

with SoC EDS and various components of the HPS. The HWLibs are also typically used

by Intel’s OS partners to build board support packages for operating systems.

The HWLibs have two components:

•

SoC Abstraction Layer (SoCAL): Symbolic register abstraction later that enables

direct access and control of HPS device registers within the address space.

•

Hardware Manager (HWMgr): APIs that provide more complex functionality and

drivers for higher level use case scenarios.

5. Embedded Software Design Guidelines for SoC FPGAs

AN-796 | 2018.06.18

AN 796: Cyclone V and Arria V SoC Device Design Guidelines

57