Error Messages and Beep Codes

105

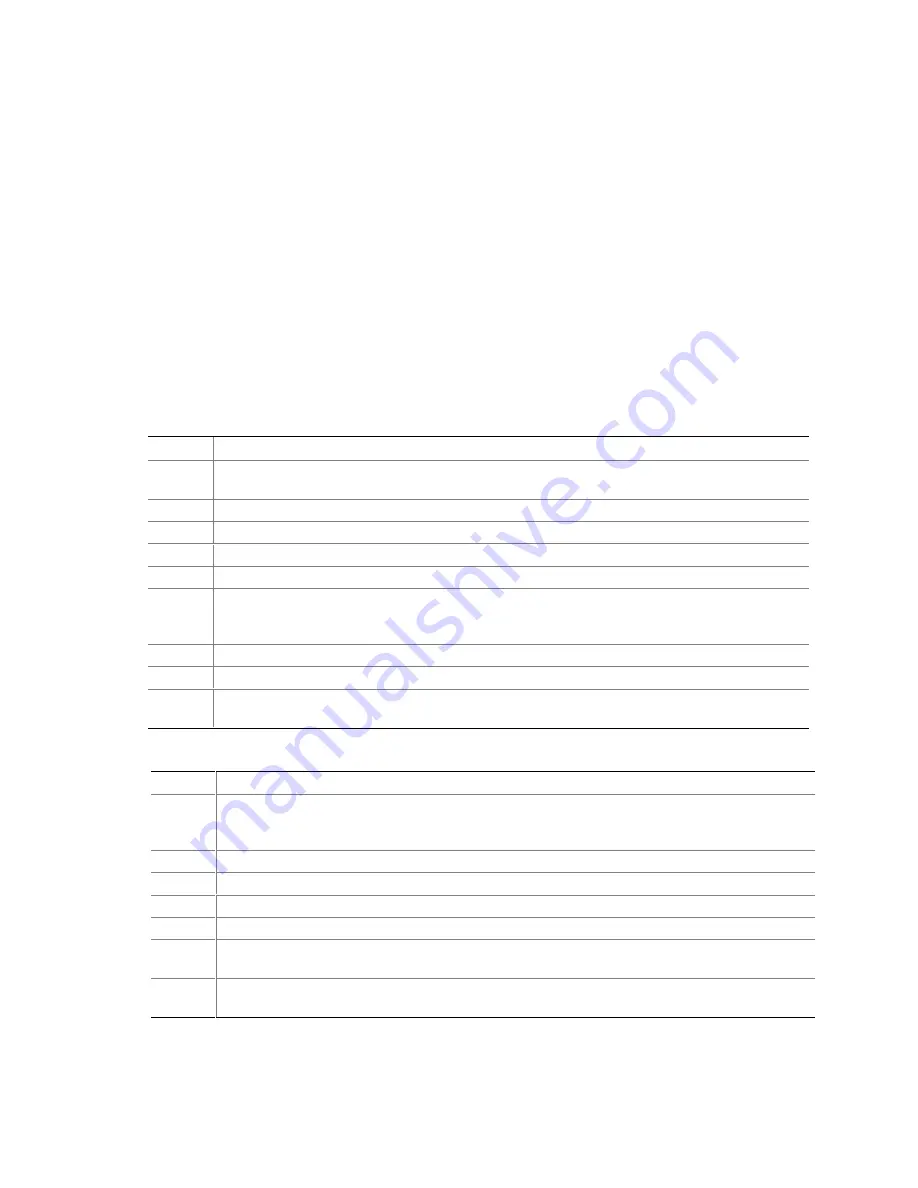

5.2 Port 80h POST Codes

During the POST, the BIOS generates diagnostic progress codes (POST codes) to I/O port 80h. If

the POST fails, execution stops and the last POST code generated is left at port 80h. This code is

useful for determining the point where an error occurred.

Displaying the POST codes requires an add-in card (often called a POST card). The POST card

can decode the port and display the contents on a medium such as a seven-segment display. These

cards can be purchased from JDR Microdevices or other sources.

The tables below offer descriptions of the POST codes generated by the BIOS. Table 75 defines

the Uncompressed INIT Code Checkpoints,

Table 76 describes the Boot Block Recovery Code Checkpoints, and Table 77 lists the Runtime

Code Uncompressed in F000 Shadow RAM. Some codes are repeated in the tables because that

code applies to more than one operation.

Table 75. Uncompressed INIT Code Checkpoints

Code

Description of POST Operation

D0

NMI is disabled. Onboard keyboard controller and real time clock enabled (if present).

Initialization code checksum verification starting.

D1

Keyboard controller BAT test, CPU ID saved, and going to 4 GB flat mode.

D3

Initialize chipset, start memory refresh, and determine memory size.

D4

Verify base memory.

D5

Initialization code to be copied to segment 0 and control to be transferred to segment 0.

D6

Control is in segment 0. Used to check if in recovery mode and to verify main BIOS checksum.

If in recovery mode or if main BIOS checksum is wrong, go to check point E0 for recovery.

Otherwise, go to check point D7 to give control to main BIOS.

D7

Find main BIOS module in ROM image.

D8

Uncompress the main BIOS module.

D9

Copy main BIOS image to F000 shadow RAM and give control to main BIOS in F000

shadow RAM.

Table 76. Boot Block Recovery Code Checkpoints

Code

Description of POST Operation

E0

Onboard diskette controller (if any) is initialized. Compressed recovery code is uncompressed at

F000:0000 in shadow RAM. Give control to recovery code at F000 in shadow RAM. Initialize

interrupt vector tables, system timer, DMA controller, and interrupt controller.

E8

Initialize extra (Intel recovery) module.

E9

Initialize diskette drive.

EA

Try to boot from diskette. If reading of boot sector is successful, give control to boot sector code.

EB

Boot from diskette failed; look for ATAPI (LS-120, Zip) devices.

EC

Try to boot from ATAPI device. If reading of boot sector is successful, give control to boot sector

code.

EF

Boot from diskette and ATAPI device failed. Give two beeps. Retry the booting procedure (go to

check point E9).