INSTRUCTION SET REFERENCE

6-114

6.2.67

sysctl

Mnemonic:

sysctl

System Control

Format:

sysctl

src1,

src2,

src/dst

reg/lit

reg/lit

reg

Description:

Performs system management and control operations including requesting

software interrupts, invalidating the instruction cache, configuring the

instruction cache, processor reinitialization, modifying memory-mapped

registers, and acquiring breakpoint resource information.

Processor control function specified by the message field of src1 is executed.

The type field of src1 is interpreted depending upon the command.

Remaining src1 bits are reserved. The src2 and src3 operands are also

interpreted depending upon the command.

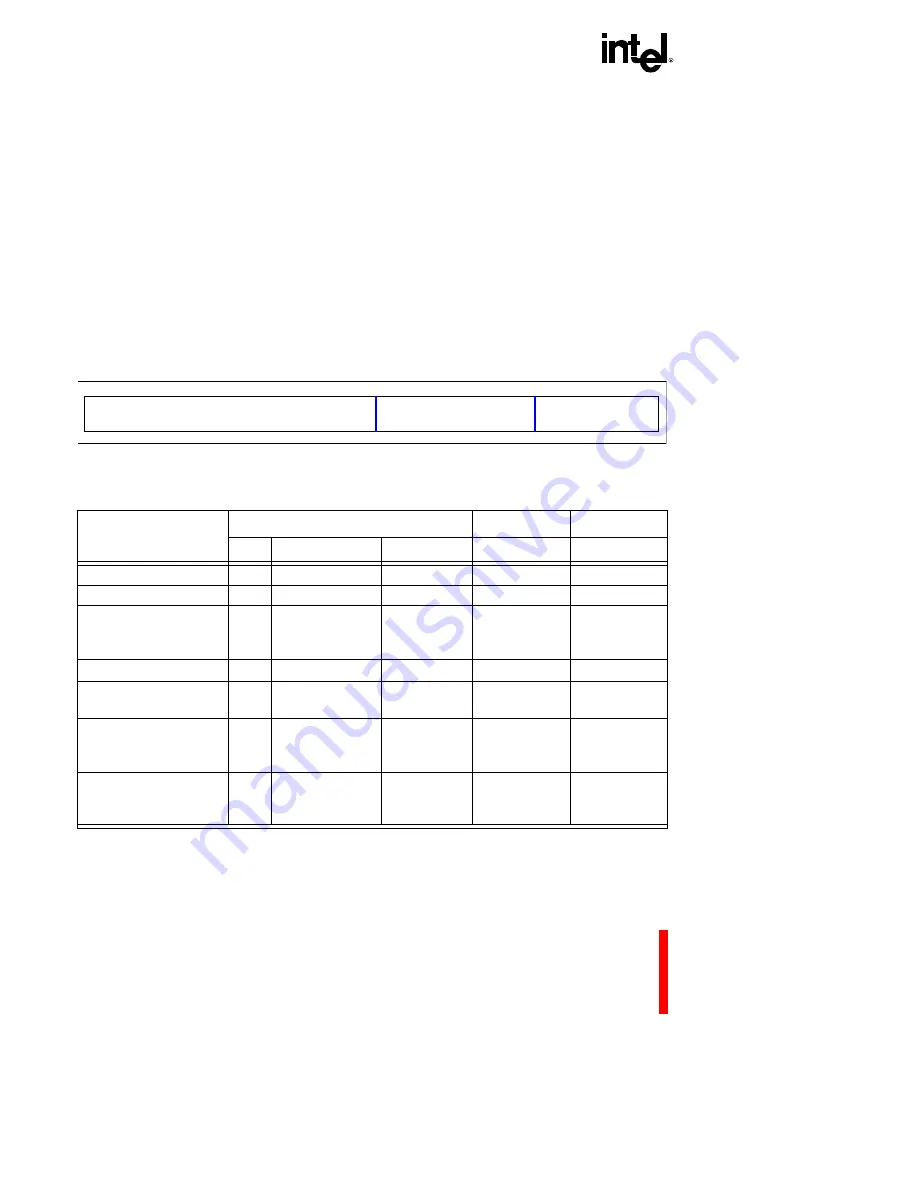

Figure 6-7. Src1 Operand Interpretation

Table 6-18. sysctl Field Definitions

Message

src1

src2

src/dst

Type

Field 1

Field 2

Field 3

Field 4

Request Interrupt

0x0

Vector Number

N/U

N/U

N/U

Invalidate Cache

0x1

N/U

N/U

N/U

N/U

Configure Instruction

Cache

0x2

Cache Mode

Configuration

(See

Table 6-19

)

N/U

Cache load

address

N/U

Reinitialize

0x3

N/U

N/U

Starting IP

PRCB Pointer

Load Control Register

0x4

Register Group

Number

N/U

N/U

N/U

Modify

Memory-Mapped

Control Register (MMR)

0x5

N/U

Lower 2 bytes

of MMR

address

Value to write

Mask

Breakpoint Resource

Request

0x6

N/U

N/U

N/U

Breakpoint info

(See

Figure 6-8

)

NOTE: Sources and fields that are not used (designated N/U) are ignored.

8 7

0

31

16 15

Message Type

Field 2

Field 1

Summary of Contents for i960 Jx

Page 1: ...Release Date December 1997 Order Number 272483 002 i960 Jx Microprocessor Developer s Manual ...

Page 24: ......

Page 25: ...1 INTRODUCTION ...

Page 26: ......

Page 35: ...2 DATA TYPES AND MEMORY ADDRESSING MODES ...

Page 36: ......

Page 46: ......

Page 47: ...3 PROGRAMMING ENVIRONMENT ...

Page 48: ......

Page 73: ...4 CACHE AND ON CHIP DATA RAM ...

Page 74: ......

Page 85: ...5 INSTRUCTION SET OVERVIEW ...

Page 86: ......

Page 111: ...6 INSTRUCTION SET REFERENCE ...

Page 112: ......

Page 233: ...7 PROCEDURE CALLS ...

Page 234: ......

Page 256: ......

Page 257: ...8 FAULTS ...

Page 258: ......

Page 291: ...9 TRACING AND DEBUGGING ...

Page 292: ......

Page 309: ...10 TIMERS ...

Page 310: ......

Page 324: ......

Page 325: ...11 INTERRUPTS ...

Page 326: ......

Page 369: ...12 INITIALIZATION AND SYSTEM REQUIREMENTS ...

Page 370: ......

Page 412: ......

Page 413: ...13 MEMORY CONFIGURATION ...

Page 414: ......

Page 429: ...14 EXTERNAL BUS ...

Page 430: ......

Page 468: ......

Page 469: ...15 TEST FEATURES ...

Page 470: ......

Page 493: ...A CONSIDERATIONS FOR WRITING PORTABLE CODE ...

Page 494: ......

Page 502: ......

Page 503: ...B OPCODES AND EXECUTION TIMES ...

Page 504: ......

Page 515: ...C MACHINE LEVEL INSTRUCTION FORMATS ...

Page 516: ......

Page 523: ...D REGISTER AND DATA STRUCTURES ...

Page 524: ......

Page 550: ......

Page 551: ...GLOSSARY ...

Page 552: ......

Page 561: ...INDEX ...

Page 562: ......

Page 578: ......