Hardware Design Guide

113

IXP28XX Network Processor

PCI

Table 39

provides routing guidelines for the PPCI address/data group parameters.

6.2.1.2

PPCI Clock Signals

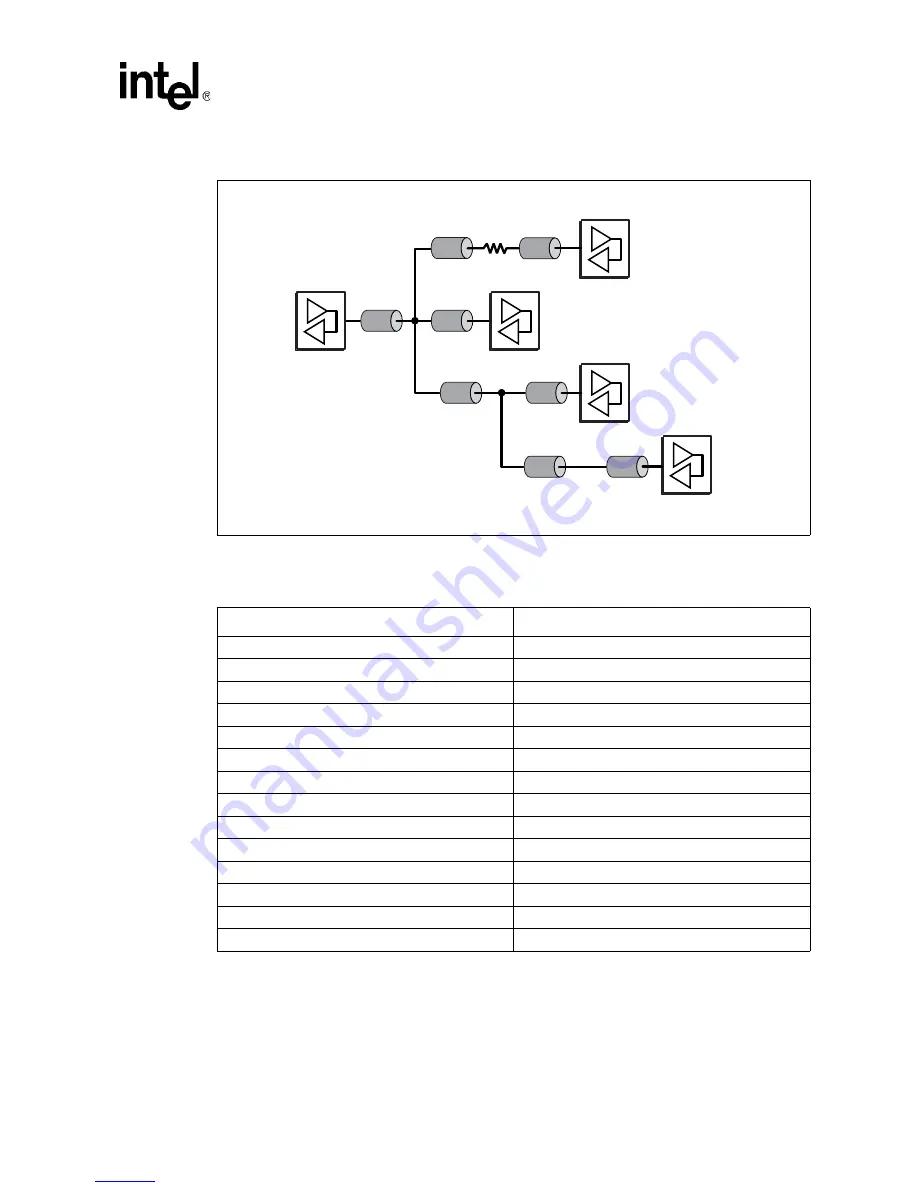

Figure 65

illustrates the topology for PPCI clock signals. All of the clock signal traces for the PPCI

bus should be matched.

Figure 64.

PPCI Address/Data Signal Topology

!"

#

$

%

!

Table 39.

PPCI Address/Data Group Guidelines

Parameter

Routing Guidelines

Signal Group

Address/Data

Topology

Daisy Chain

Reference Plane

Dual-referenced, PWR–SIG–GND

Characteristic Trace Impedance

60

Ω

± 10%

Nominal Trace Width

3.5 mils

Nominal Trace Separation

9.0 mils

Spacing to Other Groups

20 mils

Trace Length A

Maximum = 50 mils

Trace Length B

Maximum = 4200 mils

Trace Length C

Maximum = 4500 mils

Trace Length D

Maximum = 50 mils

Trace Length E

Maximum = 1200 mils

Trace Length F

Maximum = 2500 mils

Maximum Via Count per Signal

8 Vias

Downloaded from

Elcodis.com

electronic components distributor