5-8

BUS TRANSACTIONS AND OPERATIONS

These transactions drive REQa[0]#active if request initiated data is being sent. The Central

Agent will then drive TRDY#.

5.2.3.1.

REQUEST INITIATOR RESPONSIBILITIES

Generate the request with valid encodings. The reserved fields are driven inactive.

5.2.3.2.

CENTRAL AGENT RESPONSIBILITIES

Generate response for all encodings including all reserved encodings. Return data as necessary

5.2.3.3.

OBSERVING AGENT RESPONSIBILITIES

Observing agents must decode the entire request field and determine if they are required to take

any action. Of course, any agent may stall the Snoop Result Phase to delay completion.

5.2.3.4.

INTERRUPT ACKNOWLEDGE TRANSACTION

A processor agent issues an Interrupt Acknowledge Transaction in response to an interrupt from

an 8259A or similar interrupt controller. The response agent (normally the I/O agent) must per-

form whatever handshaking the interrupt controller requires. For example, an I/O agent inter-

faced to an 8259A interrupt controller must issue two locked-interrupt-acknowledge cycles to

the 8259A to process one Interrupt Acknowledge Transaction it receives from a Pentium Pro

processor. The I/O agent returns the interrupt vector generated by the 8259A to the processor as

a single data-cycle response on D[7:0]#. D[63:8]# are undefined. Note that the BE[7:0]# field

reflects this. The address Aa[35:3]# signals are reserved and can be driven to any value.

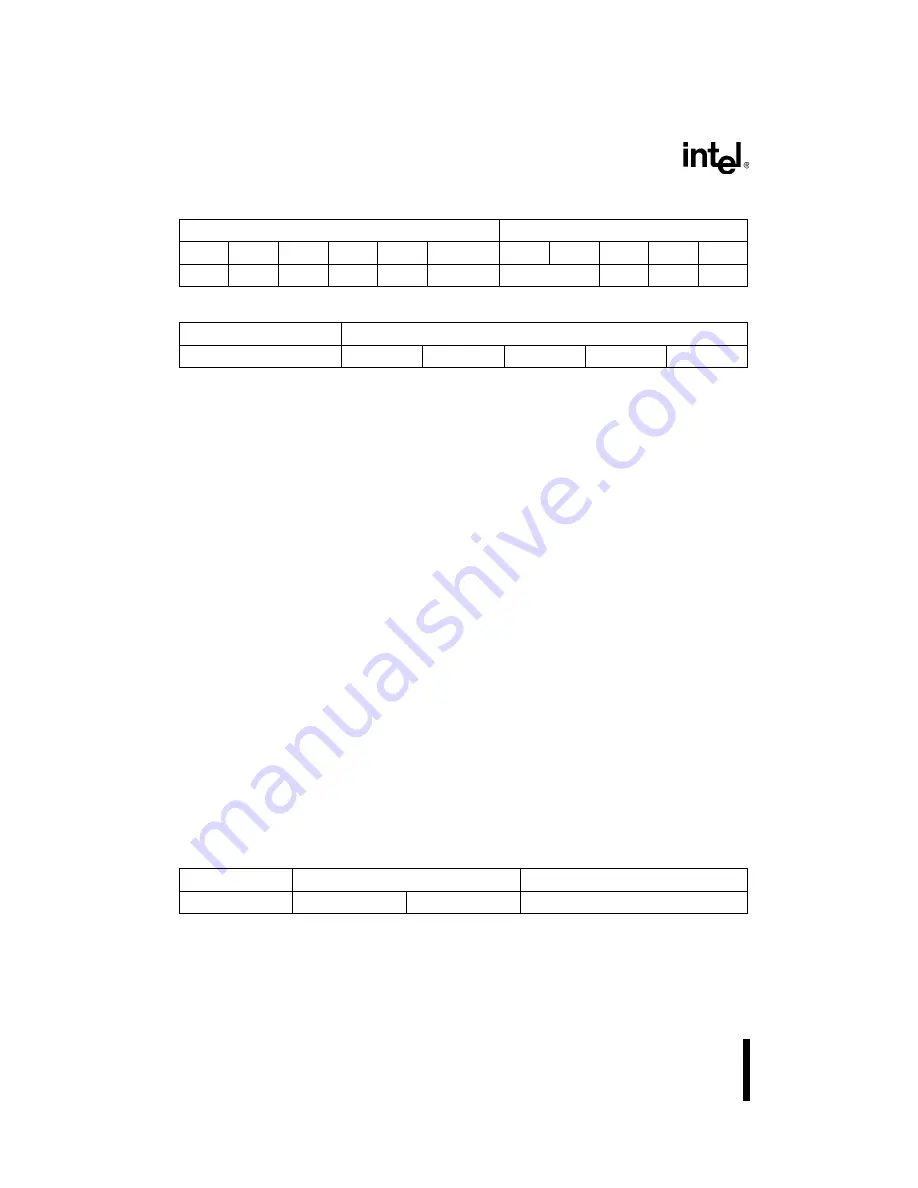

REQa[4:0]#

REQb[4:0]#

read

0

1

0

0

W/R#=0

write

0

1

0

0

W/R#=1

DSZ[1:0]#

rsvd

x

x

Ab[15:8]#

Ab[7:3]#

x

SMMEM#

SPLCK#=0

rsvd

DEN#

rsvd

REQa[0]#

REQb[1:0]#

Ab[15:8]#

0

0

0

01

Summary of Contents for Pentium Pro Family

Page 17: ...1 Component Introduction ...

Page 26: ...2 Pentium Pro Processor Architecture Overview ...

Page 27: ......

Page 36: ...3 Bus Overview ...

Page 62: ...4 Bus Protocol ...

Page 105: ...5 Bus Transactions and Operations ...

Page 126: ...6 Range Registers ...

Page 131: ...7 Cache Protocol ...

Page 135: ...8 Data Integrity ...

Page 148: ...9 Configuration ...

Page 161: ...10 Pentium Pro Processor Test Access Port TAP ...

Page 172: ...11 Electrical Specifications ...

Page 201: ...12 GTL Interface Specification ...

Page 229: ...13 3 3V Tolerant Signal Quality Specifications ...

Page 233: ...14 Thermal Specifications ...

Page 239: ...15 Mechanical Specifications ...

Page 241: ...15 2 MECHANICAL SPECIFICATIONS s Figure 15 1 Package Dimensions Bottom View ...

Page 252: ...16 Tools ...

Page 260: ...16 8 TOOLS Figure 16 4 Generic MP System Layout for Debug Port Connection ...

Page 264: ...17 OverDrive Processor Socket Specification ...

Page 290: ...A Signals Reference ...

Page 320: ...Index ...

Page 328: ......