11-6

ELECTRICAL SPECIFICATIONS

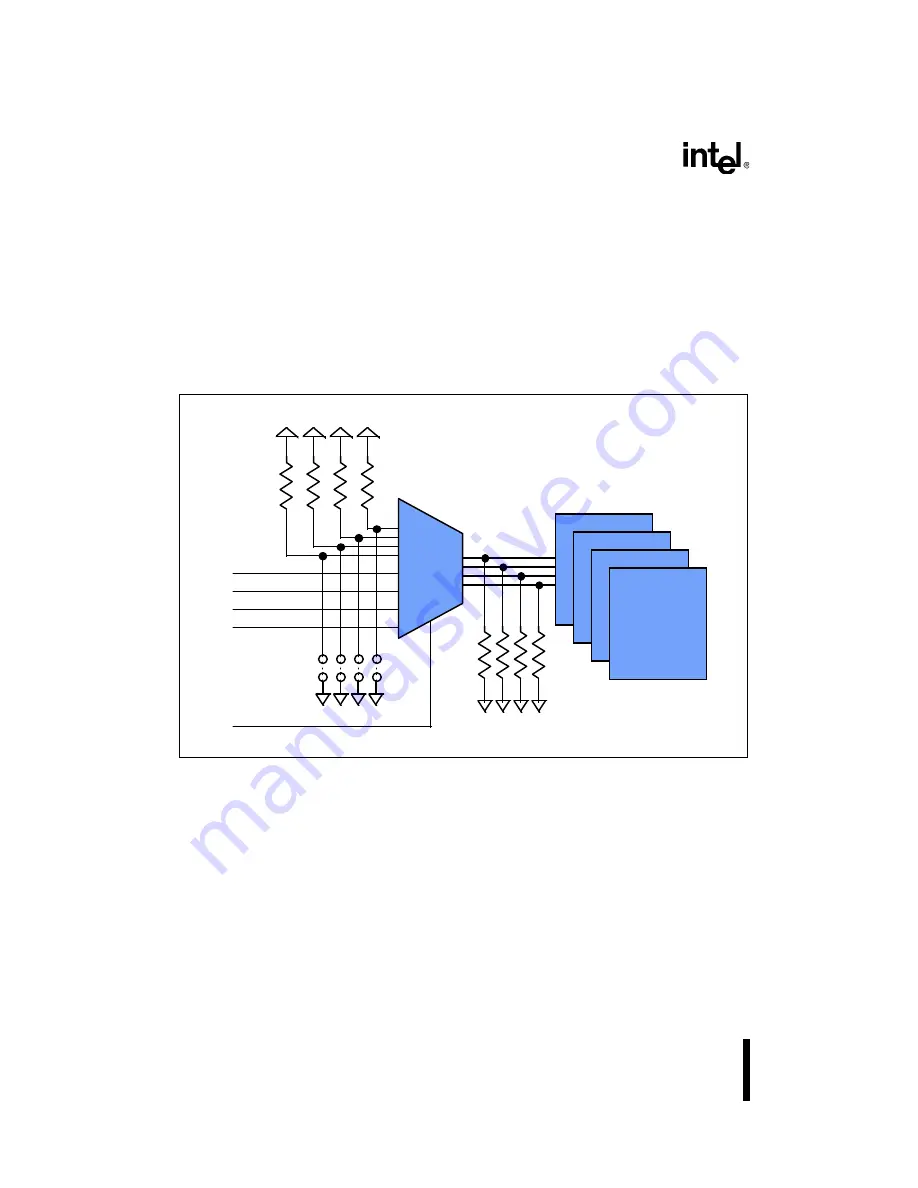

Using CRESET# (CMOS reset), the circuit in Figure 11-4 can be used to share the pins. The pins

of the processors are bussed together to allow any one of them to be the compatibility processor.

The component used as the multiplexer must not be powered by more than 3.3V in order to meet

the Pentium Pro processor’s 3.3V tolerant buffer specifications. The multiplexer output current

should be limited to 200mA max, in case the VccP supply ever fails to the processor.

The pull-down resistors between the multiplexer and the processor (1K

Ω

) force a ratio of 2x into

the processor in the event that the Pentium Pro processor powers up before the multiplexer

and/or the chipset. This prevents the processor from ever seeing a ratio higher than the final

ratio.

If the multiplexer were powered by VccP, CRESET# would still be unknown until the 3.3V sup-

ply came up to power the CRESET# driver. A pull-down can be used on CRESET# instead of

the four between the multiplexer and the Pentium Pro processor in this case. In this case, the

multiplexer must be designed such that the compatibility inputs are truly ignored as their state

is unknown.

In any case, the compatibility inputs to the multiplexer must meet the input specifications of the

multiplexer. This may require a level translation before the multiplexer inputs unless the inputs

and the signals driving them are already compatible.

For FRC mode processors, one multiplexer will be needed per FRC pair, and the multiplexer will

need to be clocked using BCLK to meet setup and hold times to the processors. This may require

the use of high speed programmable logic.

Figure 11-4. Example Schematic for Clock Ratio Pin Sharing

A20M#

IGNNE#

LINT1/NMI

LINT0/INTR

Set Ratio:

P6

CRESET#

P6

P6

Pentium

®

Pro

Processor

1K

Ω

3.3V

Mux

1K

Ω

3.3V

Summary of Contents for Pentium Pro Family

Page 17: ...1 Component Introduction ...

Page 26: ...2 Pentium Pro Processor Architecture Overview ...

Page 27: ......

Page 36: ...3 Bus Overview ...

Page 62: ...4 Bus Protocol ...

Page 105: ...5 Bus Transactions and Operations ...

Page 126: ...6 Range Registers ...

Page 131: ...7 Cache Protocol ...

Page 135: ...8 Data Integrity ...

Page 148: ...9 Configuration ...

Page 161: ...10 Pentium Pro Processor Test Access Port TAP ...

Page 172: ...11 Electrical Specifications ...

Page 201: ...12 GTL Interface Specification ...

Page 229: ...13 3 3V Tolerant Signal Quality Specifications ...

Page 233: ...14 Thermal Specifications ...

Page 239: ...15 Mechanical Specifications ...

Page 241: ...15 2 MECHANICAL SPECIFICATIONS s Figure 15 1 Package Dimensions Bottom View ...

Page 252: ...16 Tools ...

Page 260: ...16 8 TOOLS Figure 16 4 Generic MP System Layout for Debug Port Connection ...

Page 264: ...17 OverDrive Processor Socket Specification ...

Page 290: ...A Signals Reference ...

Page 320: ...Index ...

Page 328: ......