1-5

COMPONENT INTRODUCTION

1.2.4.

Data Integrity

The Pentium Pro processor bus provides parity signals for address, request, and response sig-

nals. The bus protocol supports retrying bus requests.

The Pentium Pro processor bus supports error correcting code (ECC) on the data bus and has

correction capability at the receiver.

The Pentium Pro processor supports functional redundancy checking (FRC), similar to that of

the Pentium processor. FRC support enables the Pentium Pro processor to be used in high data-

integrity, fault-tolerant applications. In addition, two Pentium Pro processors can be configured

at power-on as an FRC pair or a multiprocessor-ready pair.

1.3.

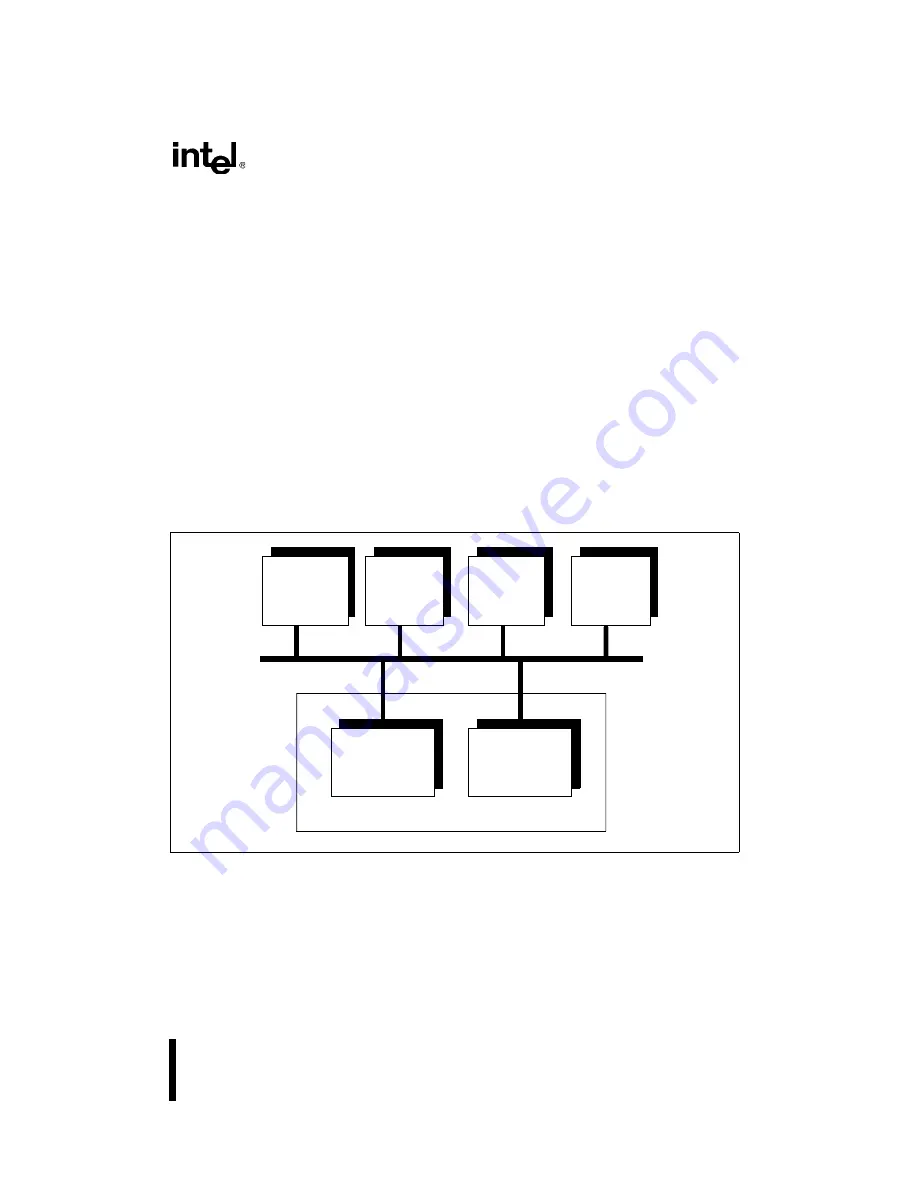

SYSTEM OVERVIEW

Figure 1-2 illustrates the Pentium Pro processor system environment, containing multiple pro-

cessors (MP), memory, and I/O. This particular architectural view is not intended to imply any

implementation trade-offs.

Figure 1-2. Pentium

®

Pro Processor System Interface Block Diagram

P6

Pentium

®

Pro

Agent 0

Pentium Pro

Agent 2

Pentium Pro

Agent 1

Pentium Pro

Agent 3

High Speed I/O

Interface

Memory

Interface

System Interface

Processor

Processor

Processor

Processor

Summary of Contents for Pentium Pro Family

Page 17: ...1 Component Introduction ...

Page 26: ...2 Pentium Pro Processor Architecture Overview ...

Page 27: ......

Page 36: ...3 Bus Overview ...

Page 62: ...4 Bus Protocol ...

Page 105: ...5 Bus Transactions and Operations ...

Page 126: ...6 Range Registers ...

Page 131: ...7 Cache Protocol ...

Page 135: ...8 Data Integrity ...

Page 148: ...9 Configuration ...

Page 161: ...10 Pentium Pro Processor Test Access Port TAP ...

Page 172: ...11 Electrical Specifications ...

Page 201: ...12 GTL Interface Specification ...

Page 229: ...13 3 3V Tolerant Signal Quality Specifications ...

Page 233: ...14 Thermal Specifications ...

Page 239: ...15 Mechanical Specifications ...

Page 241: ...15 2 MECHANICAL SPECIFICATIONS s Figure 15 1 Package Dimensions Bottom View ...

Page 252: ...16 Tools ...

Page 260: ...16 8 TOOLS Figure 16 4 Generic MP System Layout for Debug Port Connection ...

Page 264: ...17 OverDrive Processor Socket Specification ...

Page 290: ...A Signals Reference ...

Page 320: ...Index ...

Page 328: ......