A-19

SIGNALS REFERENCE

A.1.43. RESET# (I)

The RESET# signal is the Execution Control group reset signal. Asserting RESET# resets all

Pentium Pro processors to known states and invalidates their L1 and L2 caches without writing

back Modified (M state) lines. RESET# must remain active for one microsecond for a “warm”

reset. For a power-on type reset, RESET# must stay active for at least one millisecond after Vcc

and CLK have reached their proper DC and AC specifications. On observing active RESET#,

all bus agents must deassert their outputs within two clocks.

A number of bus signals are sampled at the active-to-inactive transition of RESET# for the pow-

er-on configuration. The configuration options are described in Chapter 9, Configuration and in

every signal description in this chapter.

Unless its outputs are tristated during power-on configuration, after active-to-inactive transition

of RESET#, the Pentium Pro processor optionally executes its built-in self-test (BIST) and be-

gins program execution at reset-vector 0_000F_FFF0H or 0_FFFF_FFF0H.

A.1.44. RP# (I/O)

The RP# signal is the Request Parity signal. It is driven by the request initiator in both clocks of

the Request Phase. RP# provides parity protection on ADS# and REQ[4:0]#. When a Pentium

Pro processor bus agent observes an RP# parity error on any one of the two Request Phase

clocks, it must assert AERR# in the Error Phase, provided “AERR# drive” is enabled during the

power-on configuration.

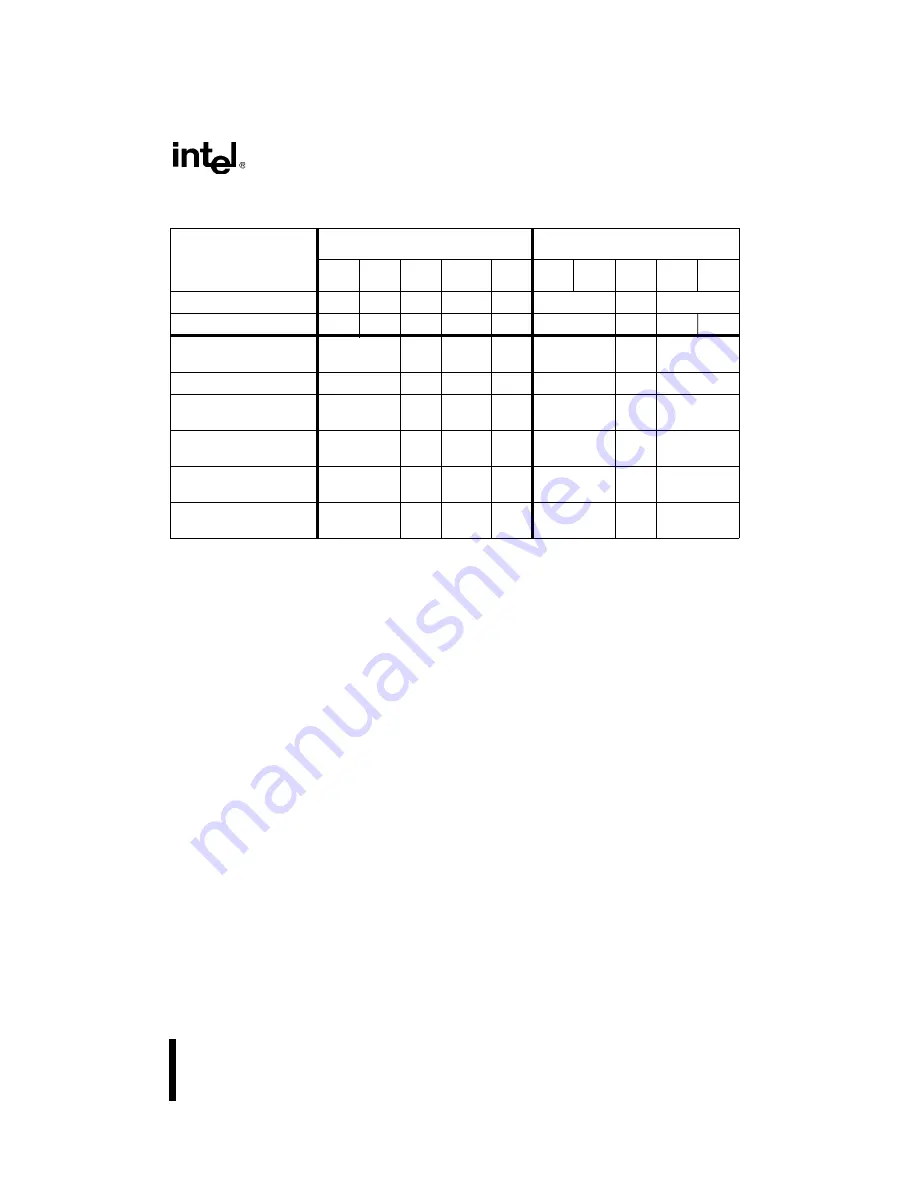

I/O Write

1

0

0

0

1

DSZ#

x

LEN#

Rsvd

(Ignore)

1

1

0

0

x

DSZ#

x

x

x

Memory Read &

Invalidate

ASZ#

0

1

0

DSZ#

x

LEN#

Rsvd

(Memory Write)

ASZ#

0

1

1

DSZ#

x

LEN#

Memory Code Read

ASZ#

1

D/C#=

0

0

DSZ#

x

LEN#

Memory Data Read

ASZ#

1

D/C#=

1

0

DSZ#

x

LEN#

Memory Write (may not

be retried)

ASZ#

1

W/WB

#=0

1

DSZ#

x

LEN#

Memory Write (may be

retried)

ASZ#

1

W/WB

#=1

1

DSZ#

x

LEN#

Table A-9. Transaction Types Defined by REQa#/REQb# Signals

Transaction

REQa[4:0]# REQb[4:0]#

4

3

2

1

0

4

3

2

1

0

Summary of Contents for Pentium Pro Family

Page 17: ...1 Component Introduction ...

Page 26: ...2 Pentium Pro Processor Architecture Overview ...

Page 27: ......

Page 36: ...3 Bus Overview ...

Page 62: ...4 Bus Protocol ...

Page 105: ...5 Bus Transactions and Operations ...

Page 126: ...6 Range Registers ...

Page 131: ...7 Cache Protocol ...

Page 135: ...8 Data Integrity ...

Page 148: ...9 Configuration ...

Page 161: ...10 Pentium Pro Processor Test Access Port TAP ...

Page 172: ...11 Electrical Specifications ...

Page 201: ...12 GTL Interface Specification ...

Page 229: ...13 3 3V Tolerant Signal Quality Specifications ...

Page 233: ...14 Thermal Specifications ...

Page 239: ...15 Mechanical Specifications ...

Page 241: ...15 2 MECHANICAL SPECIFICATIONS s Figure 15 1 Package Dimensions Bottom View ...

Page 252: ...16 Tools ...

Page 260: ...16 8 TOOLS Figure 16 4 Generic MP System Layout for Debug Port Connection ...

Page 264: ...17 OverDrive Processor Socket Specification ...

Page 290: ...A Signals Reference ...

Page 320: ...Index ...

Page 328: ......