3-13

BUS OVERVIEW

3.4.3.

Request Signals

The request signals transfer request information, including the transaction address. A Request

Phase is two clocks long beginning with the assertion of ADS#, the Address Strobe signal, as

shown in Table 3-4.

The assertion of ADS# defines the beginning of the Request Phase. The REQa[4:0]# and

Aa[35:3]# signals are valid in the clock that ADS# is asserted. The REQb[4:0]#, ATTR[7:0]#,

DID[7:0], BE[7:0]#, and the EXF[4:0]# signals are all valid in the clock after ADS# is asserted.

RP# and AP[1:0]# are valid in both clocks of the Request Phase. The LOCK# signal from the

Arbitration Phase is asserted in the clock that ADS# is asserted for a bus locked operation.

The REQa[4:0]# and the REQb[4:0]# signals identify the transaction type as defined by Table

3-5. Note that partial memory read/write transactions can be locked on the bus by asserting

the LOCK# signal. Transactions are described in detail in Chapter 5, Bus Transactions and

Operations.

NOTES:

1. These signals are driven on the indicated pin during the first clock of the Request Phase (the clock in

which ADS# is driven asserted).

2. These signals are driven on the indicated pin during the second clock of the Request Phase (the clock

after ADS# is driven asserted).

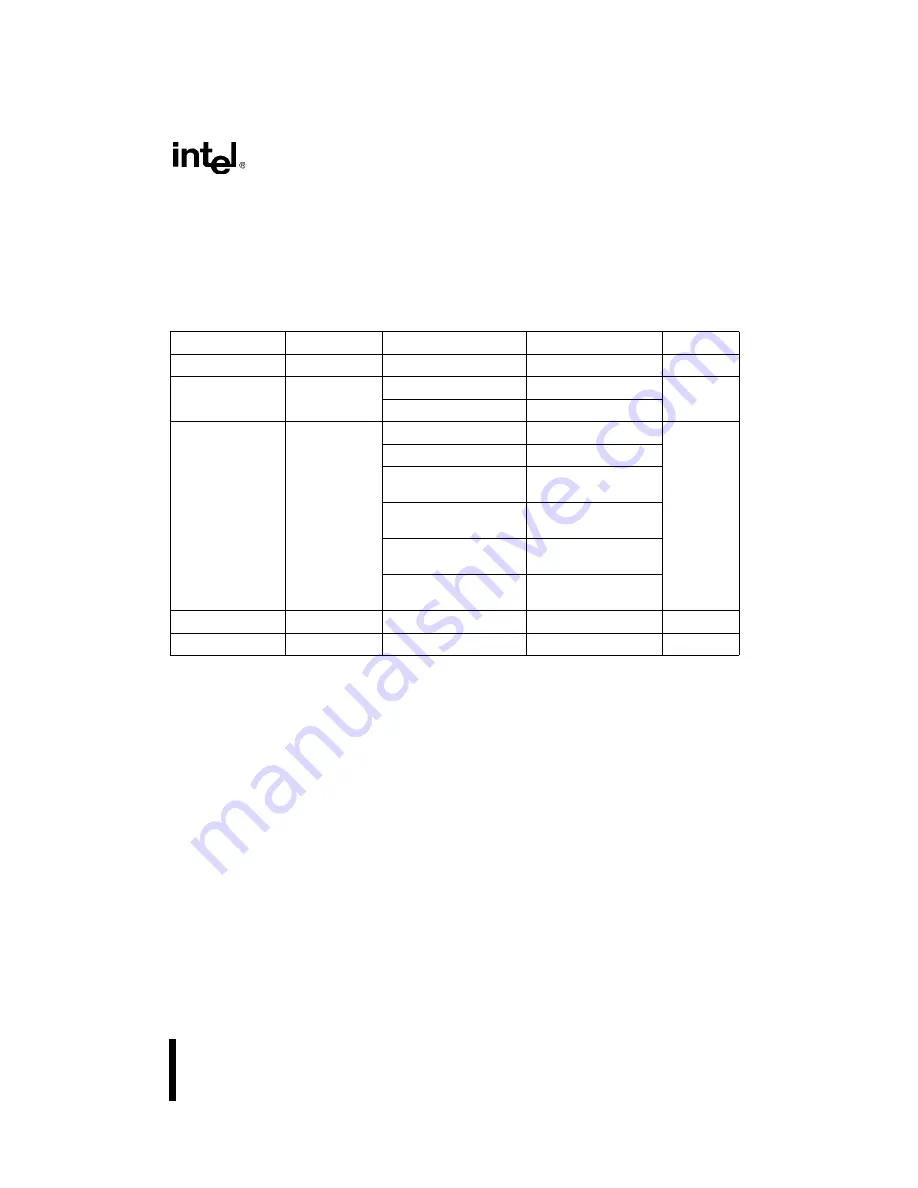

Table 3-4. Request Signals

Pin Name

Pin Mnemonic

Signal Name

Signal Mnemonic

Number

Address Strobe

ADS#

Address Strobe

ADS#

1

Request Command

REQ[4:0]#

Request1

REQa[4:0]#

5

Extended Request2

REQb[4:0]#

Address

A[35:3]#

Address1

Aa[35:3]#

33

Debug (optional)2

Ab[35:32]#

Attributes2

ATTR[7:0]# or

Ab[31:24]#

Deferred ID2

DID[7:0]# or

Ab[23:16]#

Byte Enables2

BE[7:0]# or

Ab[15:8]#

Extended Functions2

EXF[4:0]# or

Ab[7:3]#

Address Parity

AP[1:0]#

Address Parity

AP[1:0]#

2

Request Parity

RP#

Request Parity

RP#

1

Summary of Contents for Pentium Pro Family

Page 17: ...1 Component Introduction ...

Page 26: ...2 Pentium Pro Processor Architecture Overview ...

Page 27: ......

Page 36: ...3 Bus Overview ...

Page 62: ...4 Bus Protocol ...

Page 105: ...5 Bus Transactions and Operations ...

Page 126: ...6 Range Registers ...

Page 131: ...7 Cache Protocol ...

Page 135: ...8 Data Integrity ...

Page 148: ...9 Configuration ...

Page 161: ...10 Pentium Pro Processor Test Access Port TAP ...

Page 172: ...11 Electrical Specifications ...

Page 201: ...12 GTL Interface Specification ...

Page 229: ...13 3 3V Tolerant Signal Quality Specifications ...

Page 233: ...14 Thermal Specifications ...

Page 239: ...15 Mechanical Specifications ...

Page 241: ...15 2 MECHANICAL SPECIFICATIONS s Figure 15 1 Package Dimensions Bottom View ...

Page 252: ...16 Tools ...

Page 260: ...16 8 TOOLS Figure 16 4 Generic MP System Layout for Debug Port Connection ...

Page 264: ...17 OverDrive Processor Socket Specification ...

Page 290: ...A Signals Reference ...

Page 320: ...Index ...

Page 328: ......