3-16

BUS OVERVIEW

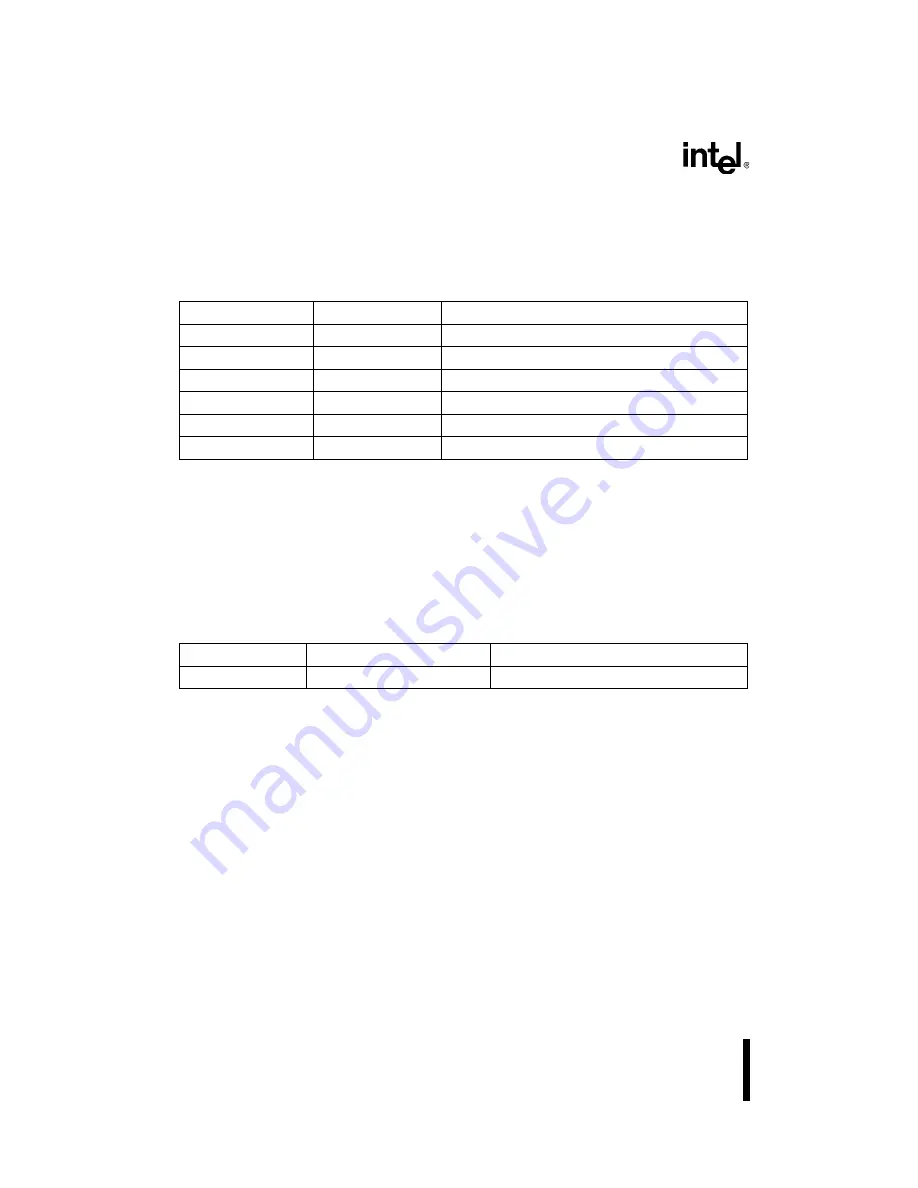

The ATTR[7:0]# pins describe the cache attributes. They are driven based on the Memory Type

Range Register attributes and the Page Table attributes as described in Table 3-8. See Chapter 6,

Range Registers for a description of the memory types.

The DID[7:0]# signals contain the request agent ID on bits DID[6:4]#, the transaction ID on

DID[3:0]#, and the agent type on DID[7]#. Symmetric agents use an agent type of 0. All priority

agents use an agent type of 1. Every deferrable transaction (DEN# asserted) issued on the Pen-

tium Pro processor bus which has not been guaranteed completion will have a unique Deferred

ID. After one of these transactions passes its Snoop Result Phase without DEFER# asserted, its

Deferred ID may be reused. During a deferred reply transaction, the Deferred ID of the agent

that deferred the original transaction is driven instead of an address.

The Byte Enables BE[7:0]# are used to determine which bytes of data should be transferred if

the data transfer is less than 8 bytes wide. BE7# applies to D[63:56], BE0# applies to D[7:0].

The byte enables are also used for special transaction encoding (see Table 3-10).

Table 3-8. Memory Range Register Signal Encoding

ATTR[7:0]#

Memory Type

Description

00000000

UC

UnCacheable

00000100

WC

Write-combining

00000101

WT

WriteThrough

00000110

WP

WriiteProtect

00000111

WB

WriteBack

All others

Reserved

Table 3-9. DID[7:0]# Encoding

DID[7]#

DID[6:4]#

DID[3:0]#

Agent Type

Agent ID

Transaction ID

Summary of Contents for Pentium Pro Family

Page 17: ...1 Component Introduction ...

Page 26: ...2 Pentium Pro Processor Architecture Overview ...

Page 27: ......

Page 36: ...3 Bus Overview ...

Page 62: ...4 Bus Protocol ...

Page 105: ...5 Bus Transactions and Operations ...

Page 126: ...6 Range Registers ...

Page 131: ...7 Cache Protocol ...

Page 135: ...8 Data Integrity ...

Page 148: ...9 Configuration ...

Page 161: ...10 Pentium Pro Processor Test Access Port TAP ...

Page 172: ...11 Electrical Specifications ...

Page 201: ...12 GTL Interface Specification ...

Page 229: ...13 3 3V Tolerant Signal Quality Specifications ...

Page 233: ...14 Thermal Specifications ...

Page 239: ...15 Mechanical Specifications ...

Page 241: ...15 2 MECHANICAL SPECIFICATIONS s Figure 15 1 Package Dimensions Bottom View ...

Page 252: ...16 Tools ...

Page 260: ...16 8 TOOLS Figure 16 4 Generic MP System Layout for Debug Port Connection ...

Page 264: ...17 OverDrive Processor Socket Specification ...

Page 290: ...A Signals Reference ...

Page 320: ...Index ...

Page 328: ......