4-23

BUS PROTOCOL

In T1, there are no transactions outstanding on the bus and {scnt} is 0. In T2, transaction 1 is

issued. In T4, as a result of the transaction driven in T2, {scnt} is incremented.

In T5, transaction 2 is issued. In T6, which is four clocks after the corresponding ADS# in T2,

the snoop results for transaction 1 are driven. In T7, {scnt} is incremented indicating that there

are two transactions on the bus that have not completed the Snoop Phase. Also in T7, the snoop

results for transaction 1 are observed. As a result, in T8, {scnt} is decremented.

In T8, the third transaction is issued. Two clocks later in T10, {scnt} is incremented. In T11,

{scnt} is decremented because the snoop results from transaction 2 are observed in T10.

In T13, the snoop results for transaction 3 are observed and in T14 {scnt} is again decremented.

4.4.2.2.

STALLED SNOOP PHASE

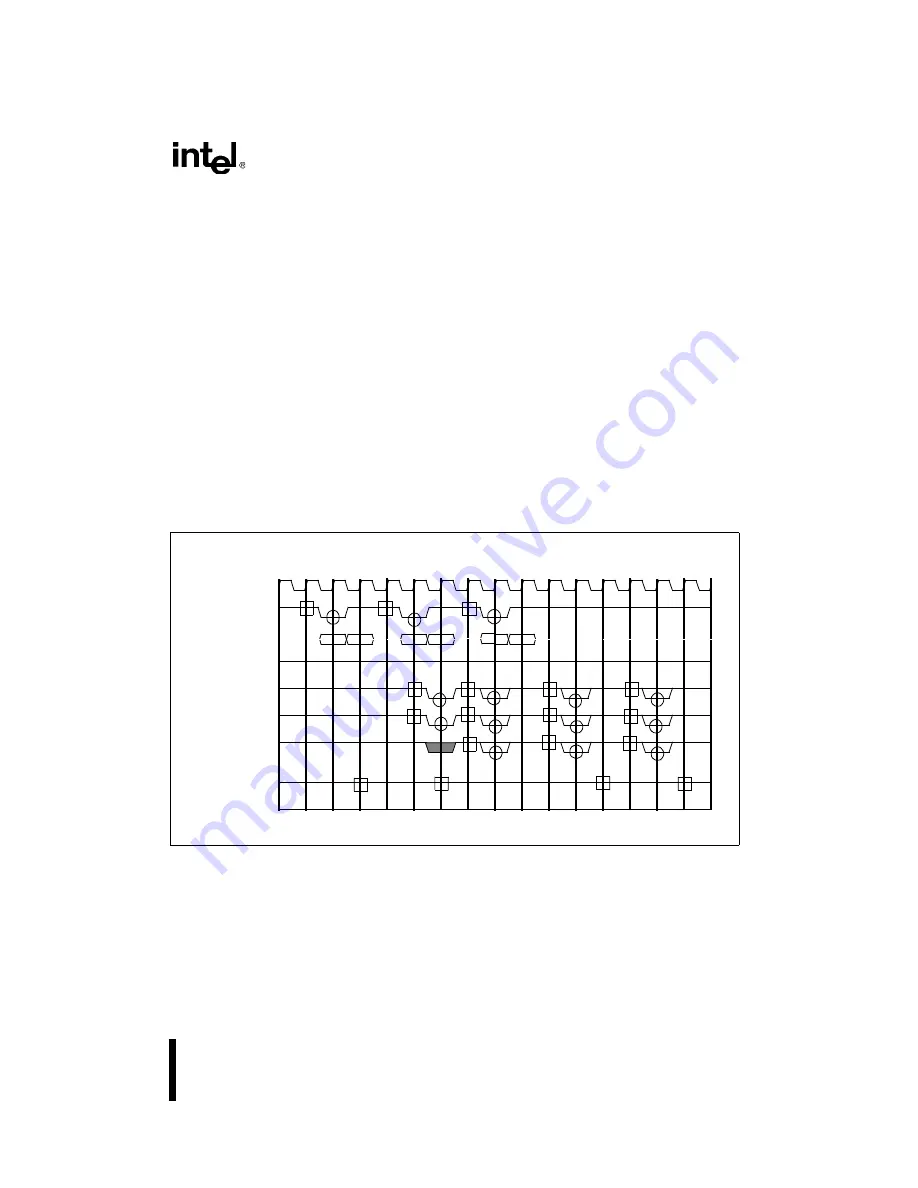

Figure 4-13 illustrates how a slower snooping agent can delay the Snoop Phase if it is unable to

deliver valid snoop results within four clocks after ADS# is asserted. The figure also illustrates

that the snoop phase of subsequent trasactions are also stalled and occur two clocks late due to

the stall of transaction one’s snoop phase.

Transactions 1, 2 and 3 are initiated with ADS# activation in T2, T5, and T8.

The Snoop Phase for transaction 1 begins in T6 four clocks from ADS#. All agents capable of

driving valid snoop response in four clocks drive appropriate levels on the snoop signals HIT#,

HITM#, and DEFER#. A slower agent that is unable to generate a snoop response in four clocks

asserts both HIT# and HITM# together in T6 to extend the Snoop Phase. Note that if the Snoop

Figure 4-13. Snoop Phase Stall Due to a Slower Agent

CLK

ADS#

{REQUEST}

HITM#

AERR#

HIT#

A

AA

AAAAAA

AA

A

AAAAAA

A

A

AAA

AA

A

AAAA

A

A

AAA

A

A

AAAAAA

1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

AA

AA

AAAAAA

A

A

AAAAAA

A

A

AAAAAA

AA

AA

AAAAAA

2

3

AA

A

AAAA

1

2

2

3

AA

A

AAAA

A

A

AAA

DEFER#

1

3

1

1

2

2

3

3

0

0

0

1

1

1

2

2

2

2

2

2

1

1

1

0

{scnt}

Summary of Contents for Pentium Pro Family

Page 17: ...1 Component Introduction ...

Page 26: ...2 Pentium Pro Processor Architecture Overview ...

Page 27: ......

Page 36: ...3 Bus Overview ...

Page 62: ...4 Bus Protocol ...

Page 105: ...5 Bus Transactions and Operations ...

Page 126: ...6 Range Registers ...

Page 131: ...7 Cache Protocol ...

Page 135: ...8 Data Integrity ...

Page 148: ...9 Configuration ...

Page 161: ...10 Pentium Pro Processor Test Access Port TAP ...

Page 172: ...11 Electrical Specifications ...

Page 201: ...12 GTL Interface Specification ...

Page 229: ...13 3 3V Tolerant Signal Quality Specifications ...

Page 233: ...14 Thermal Specifications ...

Page 239: ...15 Mechanical Specifications ...

Page 241: ...15 2 MECHANICAL SPECIFICATIONS s Figure 15 1 Package Dimensions Bottom View ...

Page 252: ...16 Tools ...

Page 260: ...16 8 TOOLS Figure 16 4 Generic MP System Layout for Debug Port Connection ...

Page 264: ...17 OverDrive Processor Socket Specification ...

Page 290: ...A Signals Reference ...

Page 320: ...Index ...

Page 328: ......