Intel® Server Board S1200SP Family Technical Product Specification

30

•

NAND/Memory interface

•

Sixteen mailbox registers for communication between the BMC and host

•

LPC ROM interface

•

BMC watchdog timer capability

•

SD/MMC card controller with DMA support

•

LED support with programmable blink rate controls on GPIOs

•

Port 80h snooping capability

•

Secondary Service Processor (SSP), which provides the HW capability of offloading time critical processing

tasks from the main ARM* core.

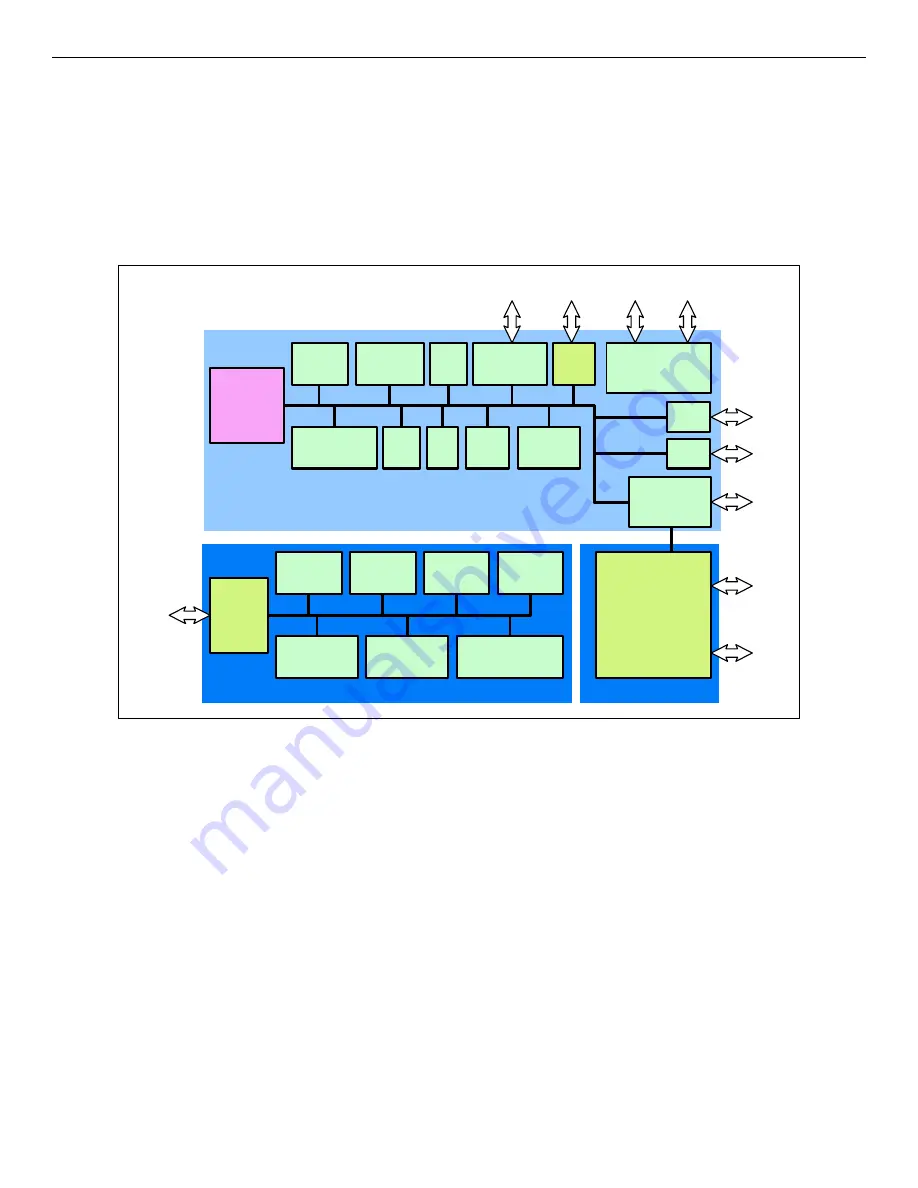

Graphics

Controller

BMC & KVMS Subsystem

Super I/O Subsystem

Graphics Subsystem

RTC &

General Purpose

TImers (6)

UART

(3)

I

2

C

(8)

Crypto

Accelerator

LPC to SPI

Flash Bridge

Watchdog

Timer

Real Time Clock

Interface

(external RTC)

LPC

Interface

To Host

RGB

Video

Output

PCIe x1

Interface

DDR-II/III

(800MHz)

JTAG

Master

BMC Boot

Flash

USB

to Host

Integrated BMC Pilot-3 Block Diagram

System

Wakeup

Control

KCS

BT &

Mailboxes

GPIO/SGPIO

UART (2)

LPC

Interface

ARM926EJ-S

16K D & I

Cache

400MHz

Interrupt

Controller

Fan Tach (16)

PWM (8)

ADC(16)

PECI3.0

10/100/1000

Ethernet MAC

with

RMII/RGMII (2)

USB 1.1

&

USB 2.0

SPI Flash

BOOT & BKUP

DDR-II/III

16-bit

Memory

Controller

JTAG

Debug

Port

JTAG

Master

LPC

Master

LPC

Master

BMC Data

Flash

RMII/RGMII

To LAN/PHY

Figure 17. Integrated BMC Functional Block Diagram

Emulex* Pilot III contains an integrated SIO, KVMS subsystem and graphics controller with the following

features:

3.5.1

Super I/O Controller

The integrated super I/O controller provides support for the following features as implemented on the server

board:

•

Keyboard Style/BT interface for BMC support

•

Two Fully Functional Serial Ports, compatible with the 16C550

•

Serial IRQ Support

•

Up to 16 Shared GPIO available for host processor

•

Programmable Wake-up Event Support

•

Plug and Play Register Set

•

Power Supply Control

Summary of Contents for S1200SPL

Page 3: ......