Functional Architecture

Intel

®

Server Board S5000VCL TPS

Revision

2.3

Intel order number: D64569-007

10

TP02091

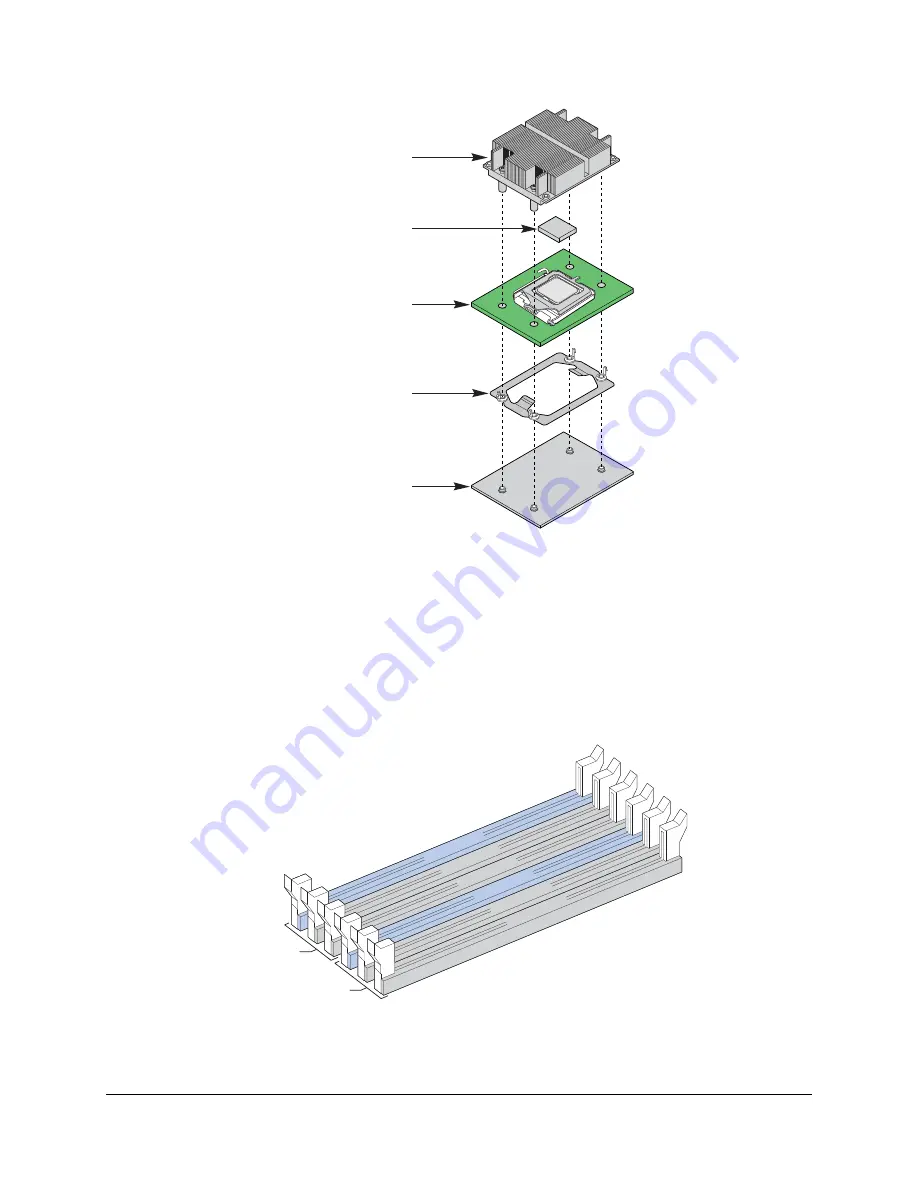

Heatsink assembly

Thermal Interface

Material (TIM)

Server Board

CEK Spring

Chassis

AF001010

Figure 5. CEK Processor Mounting

3.1.3

Memory Sub-system

The MCH masters two fully buffered DIMM (FBDIMM) memory channels. FBDIMM memory

utilizes a narrow high-speed frame-oriented interface referred to as a channel. The two

channels are routed to six DIMM slots and support registered DDR2-667 FBDIMM memory

(stacked or unstacked). Peak FBDIMM memory data bandwidth in dual channel mode is

8.0GB/s (2x4.0 GB/s) with DDR2-667/PC2-5300 (3.0 ns at CL5).

DIMM B3

DIMM B2

DIMM B1

DIMM A3

DIMM A2

DIMM A1

Channel A

Channel B

AF001011

Figure 6. Memory Layout