Intel® Server Boards SE7320SP2 and SE7525GP2

Functional Architecture

Revision 4.0

33

compatibility interrupt sources. The I/O APICs can also supply greater than 16 interrupt levels to

the processor(s). This APIC bus consists of an APIC clock and two bidirectional data lines.

3.6.3.3

Legacy Interrupt Sources

The table below recommends the logical interrupt mapping of interrupt sources. The actual

interrupt map is defined using configuration registers in the Intel

®

6300ESB I/O controller.

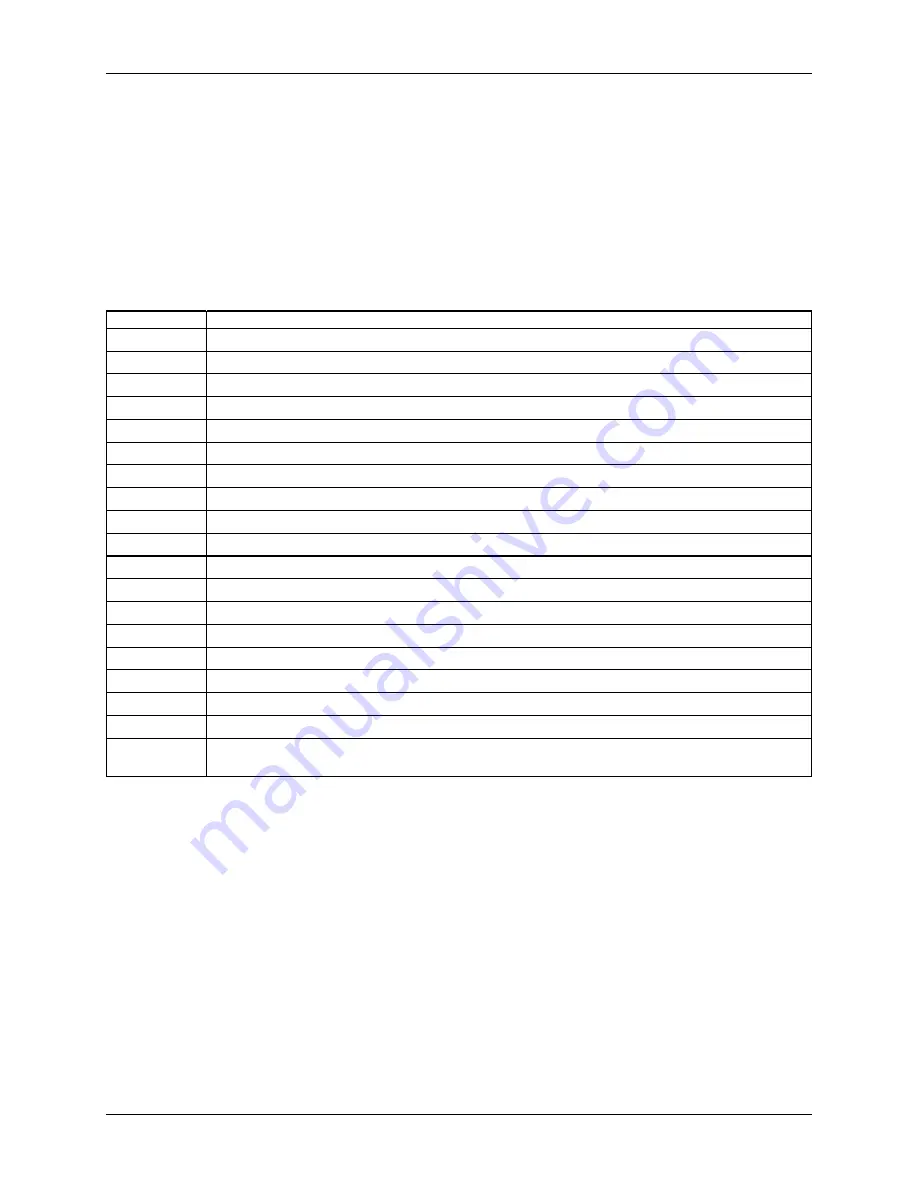

Table 12. Interrupt Definitions

ISA Interrupt

Description

INTR Processor

interrupt

NMI

NMI to processor

IRQ0 System

timer

IRQ1 Keyboard

interrupt

IRQ2 Slave

PIC

IRQ3

Serial port 1 or 2 interrupt from SUPER I/O device, user-configurable

IRQ4

Serial port 1 or 2 interrupt from SUPER I/O device, user-configurable

IRQ5

Parallel Port / Generic

IRQ6 Floppy

disk

IRQ7 Generic

IRQ8_L

Active low RTC interrupt

IRQ9 SCI*

IRQ10 Generic

IRQ11 Generic

IRQ12 Mouse

interrupt

IRQ13

Floating point processor

IRQ14

Compatibility IDE interrupt from primary channel IDE devices 0 and 1

IRQ15

Secondary IDE cable

SMI*

System management interrupt. General purpose indicator sourced by the 6300ESB to the

processors.

3.6.3.4

Serialized IRQ Support

The server boards support a serialized interrupt delivery mechanism. Serialized Interrupt

Requests (SERIRQ) consists of a start frame, a minimum of 17 IRQ / data channels, and a stop

frame. Any slave device in the quiet mode may initiate the start frame. While in the continuous

mode, the start frame is initiated by the host controller.

3.6.3.5

IRQ Scan for PCI IRQ

The IRQ / data frame structure includes the ability to handle up to 32 sampling channels with

the standard implementation using the minimum 17 sampling channels. The server boards have

an external PCI interrupt serializer for PCI IRQ scan mechanism of Intel 6300ESB I/O controller

to support 16 PCI IRQs.

Summary of Contents for SE7320SP2 - 800MHZ Ecc Ddr Xeon

Page 182: ......