Intel

®

Server Board SE7500WV2 Training

Student Workbook

36

© 2003 Intel Corporation

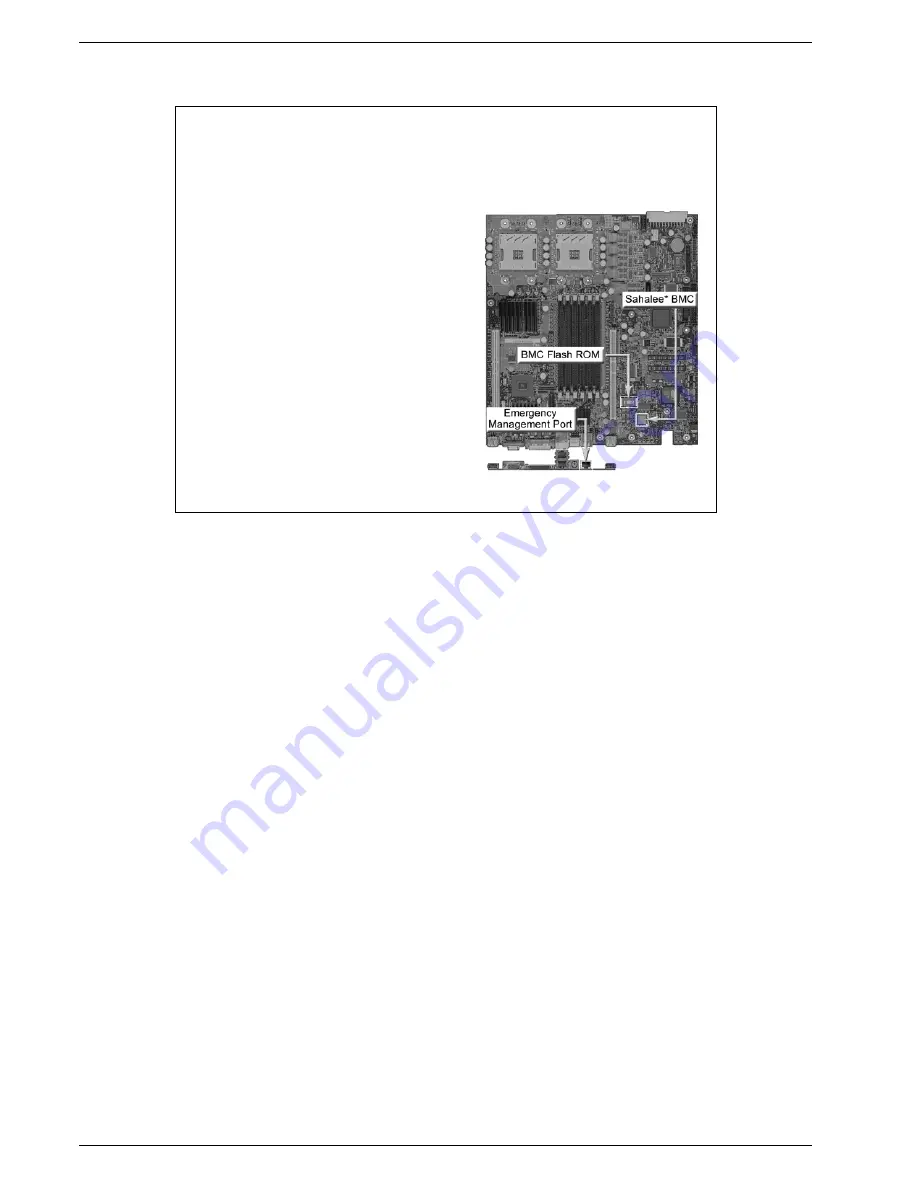

Server Management – BMC and EMP

© 2003 Intel Corporation.

*Other names and brands may be claimed as the property of others.

Intel

®

Server Board SE7500WV2

Server Management – BMC and

EMP

•

Sahalee* BMC

–

Primary management

controller

•

Emergency Management Port

–

Provides server

management when

operating system is

non-functional

•

Flash ROM

–

BMC firmware

–

System event log

–

SDR information

–

FRU information

The Intel

®

Server Board SE7500WV2 provides advanced server management features through a combination of the

server management subsystem and Intel Server Control server management software.

The server management features are implemented using the Sahalee server baseboard management controller (BMC)

chip that is connected to the ICH3 through the low pin count (LPC) bus. The BMC is an ASIC that contains a 32-bit

RISC processor core and associated peripherals used to monitor the system for critical events. Flash memory embedded

on the server board provides storage space for the BMC firmware, system event log (SEL), sensor data records (SDR)

and field replaceable unit (FRU) information.

The Sahalee* BMC works in conjunction with the Heceta* systems monitor ASIC to communicate with various sensors

and headers through the Intelligent Platform Management Bus (IPMB) to monitor:

•

All power supplies

•

SCSI termination voltage (on the SCSI version of the Intel Server Board SE7500WV2)

•

Fan tachometers and control for detecting fan failure and controlling fan speed

•

System temperature through sensors embedded in the processors and integrated into the server board, backplane and

front panel

•

Chassis intrusion

When any monitored parameter falls outside the defined thresholds, the BMC logs an event in the system event log

(SEL).

The Sahalee BMC also controls the fault resilient booting (FRB) process. If the default bootstrap processor fails to

complete the boot process, FRB attempts to boot using an alternate processor.

The Sahalee BMC provides system reset control. Reset circuitry on the Intel Server Board SE7500WV2 monitors reset

requests from the front panel, ICH3, and the processor subsystem to determine proper reset sequencing. The reset logic is

designed to accommodate a variety of reset methods:

•

Power-up reset

•

Hard reset

•

Soft reset

The emergency management port (EMP) provides out-of-band remote management of the server through the serial2 port

for serial devices, and the primary onboard NIC provides remote management functions over the LAN. This is managed

by the BMC.

Summary of Contents for SE7500WV2 - Server Chassis - SR2300

Page 1: ...Intel Server Board SE7500WV2 Training Student Workbook...

Page 6: ...Intel Server Board SE7500WV2 Training Student Workbook vi 2003 Intel Corporation...

Page 8: ...Intel Server Board SE7500WV2 Training Student Workbook 2 2003 Intel Corporation...

Page 10: ...Intel Server Board SE7500WV2 Training Student Workbook 4 2003 Intel Corporation...

Page 52: ...Intel Server Board SE7500WV2 Training Student Workbook 46 2003 Intel Corporation...

Page 110: ...Intel Server Board SE7500WV2 Training Student Workbook 104 2003 Intel Corporation...

Page 114: ...Intel Server Board SE7500WV2 Training Student Workbook 108 2003 Intel Corporation...

Page 115: ......