Intel® Server Board SE7520AF2 TPS

System BIOS

Revision 1.2

127

Intel order number C77866-003

5.11.5.1.5

SuperIO Configuration Sub-Menu

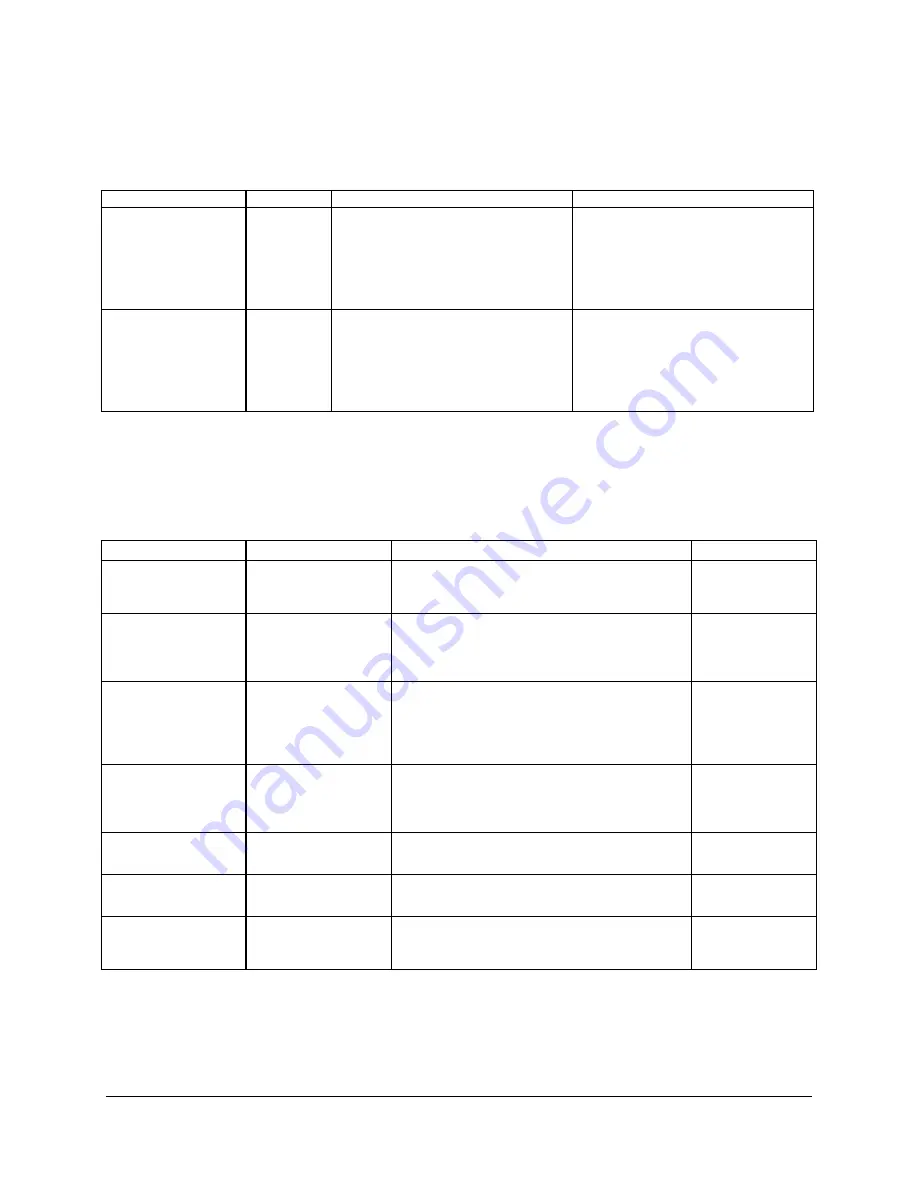

Table 46. BIOS Setup SuperIO Configuration Sub-menu

Feature

Options

Help Text

Description

Serial Port 1 Address Disabled

3F8/IRQ4

2F8/IRQ3

3E8/IRQ4

2E8/IRQ3

Allows BIOS to Select Serial Port A

Base Addresses.

Option that is used by other serial port

is hidden to prevent conflicting

settings.

Serial Port 2 Address Disabled

3F8/IRQ4

2F8/IRQ3

3E8/IRQ4

2E8/IRQ3

Allows BIOS to Select Serial Port B

Base Addresses.

Option that is used by other serial port

is hidden to prevent conflicting

settings.

5.11.5.1.6

USB Configuration Sub-Menu

Table 47. BIOS Setup USB Configuration Sub-menu Selections

Feature

Options

Help Text

Description

USB Devices

Enabled

N/A

N/A

List of USB

devices detected

by BIOS.

USB Function

Disabled

Enabled

Enables USB HOST controllers.

When set to

disabled, other

USB options are

grayed out.

Legacy USB Support Disabled

Keyboard only

Auto

Keyboard and Mouse

Enables support for legacy USB. AUTO option

disables legacy support if no USB devices are

connected. If disabled, USB Legacy Support will

not be disabled until booting an operating

system.

Port 60/64 Emulation

Disabled

Enabled

Enables I/O port 60/64h emulation support. This

should be enabled for the complete USB

keyboard legacy support for non-USB aware

OSes.

USB 2.0 Controller

Enabled

Disabled

N/A

USB 2.0 Controller

mode

FullSpeed

HiSpeed

Configures the USB 2.0 controller in HiSpeed

(480Mbps) or FullSpeed (12Mbps).

USB Mass Storage

Device Configuration

N/A

Configure the USB Mass Storage Class

Devices.

Selects submenu

with USB Device

enable.