Product Overview

Intel® Server Board SE7520BD2 Technical Product Specification

26

Revision

1.3

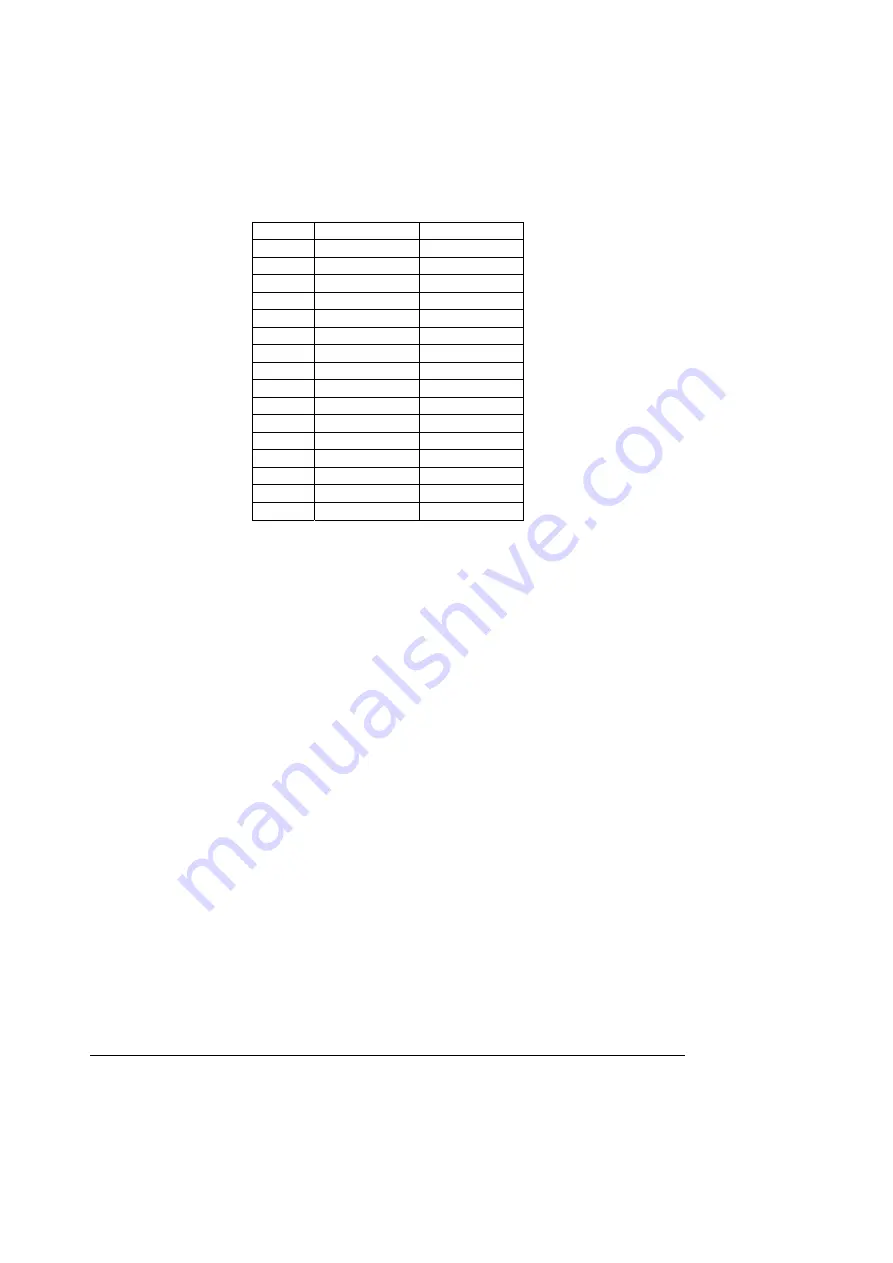

78 AD[49]/CBE[4]#

Ground

79 +VI/O

(3.3V/1.5V)

AD[48]/CBE[5]#

80 AD[47]

AD[46]

81 AD[45]

Ground

82 Ground

AD[44]

83 AD[43]

AD[42]

84 AD[41]

+VI/O

(3.3V/1.5V)

85 Ground

AD[40]

86 AD[39]

AD[38]

87 AD[37]

Ground

88 +VI/O

(3.3V/1.5V)

AD[36]

89 AD[35]

AD[34]

90 AD[33]

Ground

91 Ground

AD[32]

92

Riser Presence 1

Riser Presence 0

93 Slot2

REQ Ground

94 Ground

Slot2

GNT

Note:

The signals in red represent modifications from the standard PCI-X 2.0 pin-out; however, the PCI-X 2.0

compliant cards can still be used.

2.9.3 Ultra-320

SCSI

Controller

The Server Board SE7520BD2 provides an embedded dual-channel SCSI bus through the use

of an LSI* AIC-1030C SCSI controller. The AIC-1030C controller contains two independent

SCSI controllers that share a single 64-bit/100-MHz PCI-X mode 1 bus master interface as a

multifunction device, packaged in a 456-pin BGA. Internally, each controller is identical, capable

of operations using either 16-bit SE or LVD SCS providing 40 MBps (Ultra-wide SE), 80 MBps

(Ultra 2), 160 MBps (Ultra 160/m) or 320 MBps (Ultra 320/m). Each controller has its own set of

PCI configuration registers and SCSI I/O registers. The Server Board SE7520BD2 supports

disabling of the onboard SCSI controller through the BIOS setup menu.

The Server Board SE7520BD2 provides active terminators, termination voltage, a polyswitch

fuse, and a protection diode for both SCSI channels. By design, the onboard terminators are

enabled and no ability is provided to turn off the terminators. The user should plug-in the SCSI

devices in such a way that the SCSI controller is always at one end of the SCSI bus. This

provides either RAID 0 (integrated striping) or RAID 1/1e (integrated mirroring/enhanced)

support. The array will not span across multiple channels. All array drives need to be on one

channel only.

2.9.4

Modular RAID on Baseboard (MROMB)

The Server Board SE7520BD2 baseboard provides the hooks to support Modular RAID on

Baseboard (MROMB).

The PCI-X IRQs for slot 2 are PAIRQ<7..4>. During normal operation (no MROMB installed),

the PAIRQ 6 and 7 are shared between the SCSI device and PCI-X slot 2. When MROMB is

installed, these interrupts are disconnected from the PXH and used between the SCSI controller

and the PCI-X slot with the MROMB card. The following diagram outlines the connections on

the baseboard.