Intel® SHG2 DP Server Board Technical Product Specification

Baseboard PCI I/O Subsystem

Revision 1.0

Intel Order Number C11343-001

21

•

PCI 82550PM Network Interface Controller.

3.5.1

Device IDs (IDSEL)

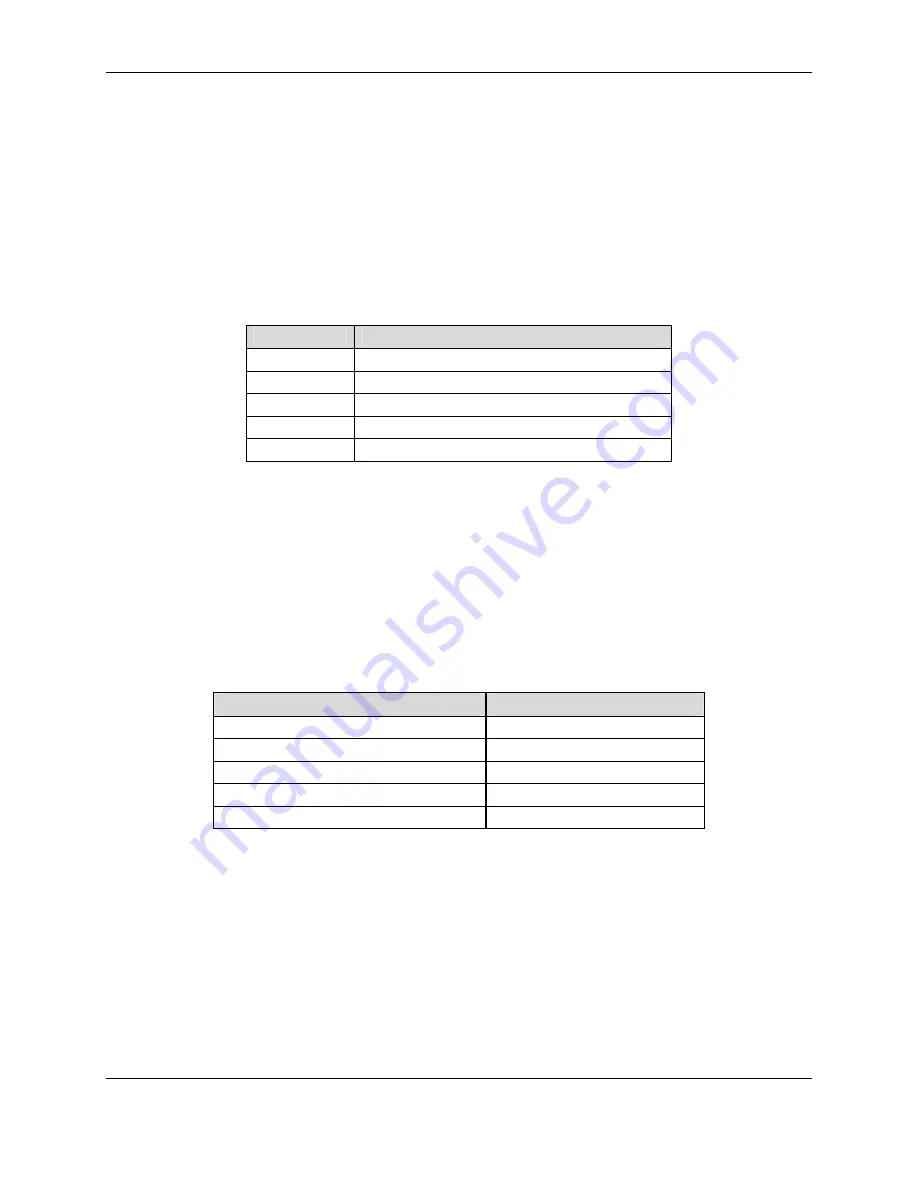

Each device under the PCI host bridge has its IDSEL signal connected to one bit of AD[31::16],

which acts as a chip select on the PCI bus segment in configuration cycles.

This determines a

unique PCI device ID value for use in configuration cycles.

Table 14

shows the bit to which

each IDSEL signal is attached for 32/33 MHz devices, and the corresponding device number.

Table 14. 32/33MHz Segment Configuration IDs

IDSEL Value

Device

24

32/33MHz Slot , PCI-3 (32/33)

25

32/33MHz Slot, PCI-4 (32/33)

20

32/33MHz Slot, PCI-5 (32/33)

19 NIC

82550PM

18

ATI RAGE* XL Video Controller

3.5.2

32/33 MHz PCI Arbitration

A 32/33 MHz segment supports five PCI masters: slots PCI-3 (32/33), PCI-4 (32/33), PCI-5

(32/33), 82550PM network controller, and the ATI RAGE* XL controller.

All PCI masters must

arbitrate for PCI access, using resources supplied by the CSB5.

The host bridge PCI interface

(CSB5) arbitration lines REQx* and GNTx* are a special case in that they are internal to the

host bridge.

Table 15

defines the arbitration connections.

Table 15. 32/33MHz Segment Arbitration Connections

Baseboard Signals

Device

D_PCIREQN/D_PCIGNTN

32/33MHz Slot, PCI-3 (32/33)

D_REQN4/D_GNTN4

32/33MHz Slot, PCI-4 (32/33)

D_REQN2/D_GNTN2

32/33MHz Slot, PCI-5 (32/33)

PCIREQN_ETHER1/PCIGNTN_ETHER1 NIC

82550PM

PCIREQN_VGA/PCIGNTN_VGA

ATI* RAGE XL

3.5.3

Network Interface Controller (NIC)

The Intel SHG2 server board supports one 10Base-T/100Base-TX network subsystem based

on the Intel 82550PM NIC. The 82550PM is a highly integrated PCI LAN controller in a thin

BGA 15 mm2 package. The controller’s baseline functionality is equivalent to that of the Intel

82559, with the addition of Alert-on-LAN functionality. The SHG2 server board supports

independent disabling of the NIC using the BIOS setup menu.

The Intel 82550PM supports the following features:

•

32-bit PCI, CardBus master interface