Intel

®

5100 Memory Controller Hub Chipset for Communications, Embedded, and Storage Applications

July 2008

TDG

Order Number: 318676-003US

5

Intel

®

5100 MCH Chipset

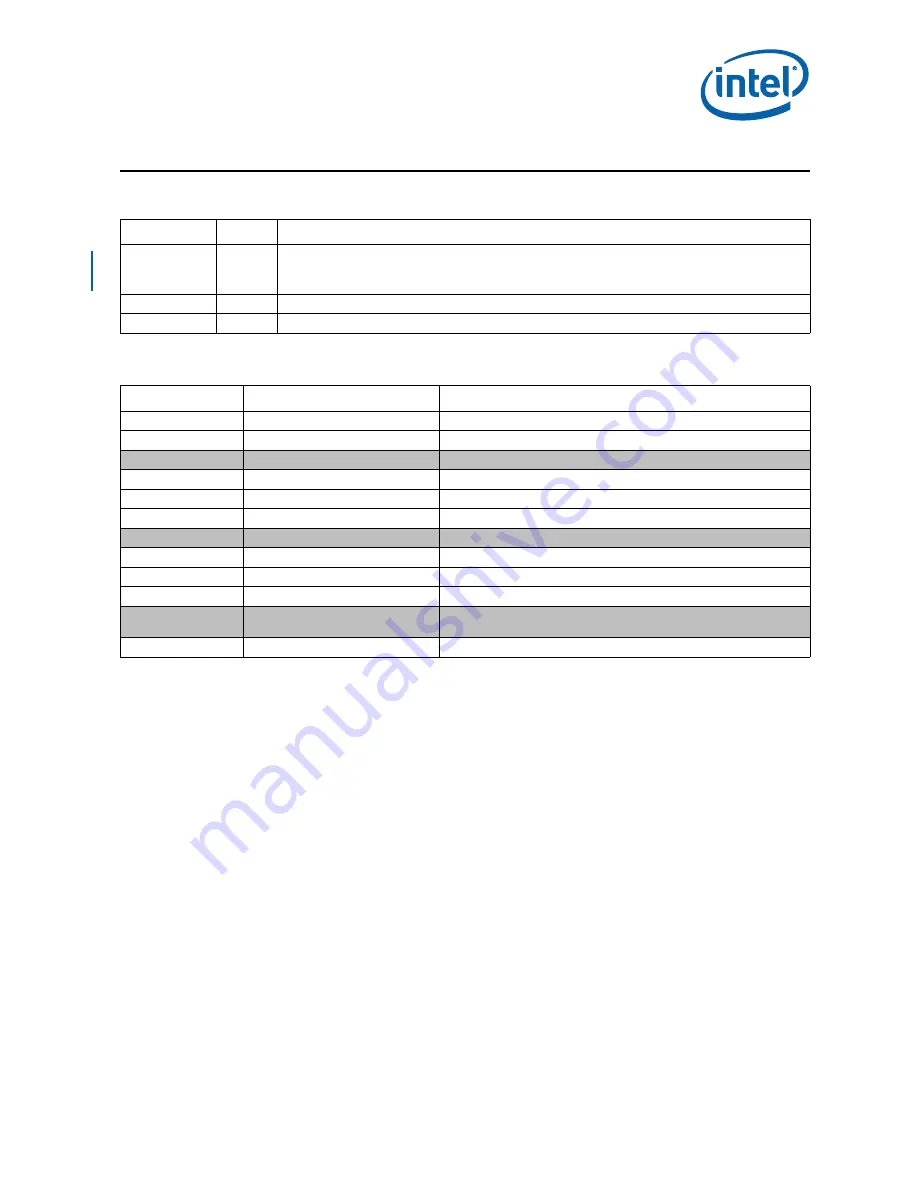

Revision History

Date

Revision Description

July 2008

003

Added the CompactPCI* reference solution

Added

Figure 26

,

Figure 27

, and

Figure 28

Updated the supplier information

February 2008

002

Updated the TDP

Max config

value to 25.7 W in

Table 3

November 2007

001

Initial release

Revision Number Descriptions

Revision

Associated Life Cycle Milestone Release Information

0.0

POP L3 Closure

Initial Documentation - Typically Internal Only

0.1–0.4

When Needed

Project Dependent - Typically Internal Only

0.5

Design Win Phase

First, Required Customer Release

0.6–0.7

When Needed

Project Dependent

0.7

Simulations Complete

Second, Recommended Customer Release

0.8–0.9

When Needed

Project Dependent

1.0

First Silicon Samples

Required Customer Release

1.1–1.4

When Needed

Project Dependent (Recommended)

1.5

Qualification Silicon Samples

Project Dependent

1.6–1.9

When Needed

Project Dependent

NDA - 2.0

Public - XXXXXX-001

First SKU Launch

Required Customer Release - Product Launch

2.1 and up

When Needed

Project Dependent

Note:

Rows highlighted in gray are required revisions.