Design Guide

19

Introduction

1.3

System Overview

The E7500 chipset is Intel’s first generation server chipset designed for use with the Xeon

processor. The architecture of the chipset provides the performance and feature-set required for

dual-processor based severs in the entry-level and mid-range, front-end and general-purpose server

market segments. A new chipset component interconnect, the Hub Interface 2.0 (HI2.0), is

designed into the E7500 chipset to provide more efficient communication between chipset

components for high-speed I/O. Each HI2.0 provides 1.066 GB/s I/O bandwidth. The E7500 MCH

has three HI2.0 connections, delivering 3.2 GB/s bandwidth for high-speed I/O, which can be used

for PCI/PCI-X bridges. The system bus, used to connect the processor with the E7500 chipset,

utilizes a 400 MHz transfer rate for data transfers, delivering 3.2 GB/s. The E7500 chipset

architecture supports a 144-bit wide, 200 MHz DDR memory interface also capable of transferring

data at 3.2 GB/s.

In addition to these performance features, E7500 chipset-based platforms also provide the RASUM

(Reliability, Availability, Serviceability, Usability, and Manageability) features required for entry-

level and mid-range servers. These features include: Chipkill* technology ECC for memory, ECC

for all high-performance I/O, out-of-band manageability through SMBus target interfaces on all

major components, memory scrubbing and auto-initialization, processor thermal monitoring, and

hot-plug PCI. For a complete list of the features on this platform, refer to the component datasheets

listed in

.

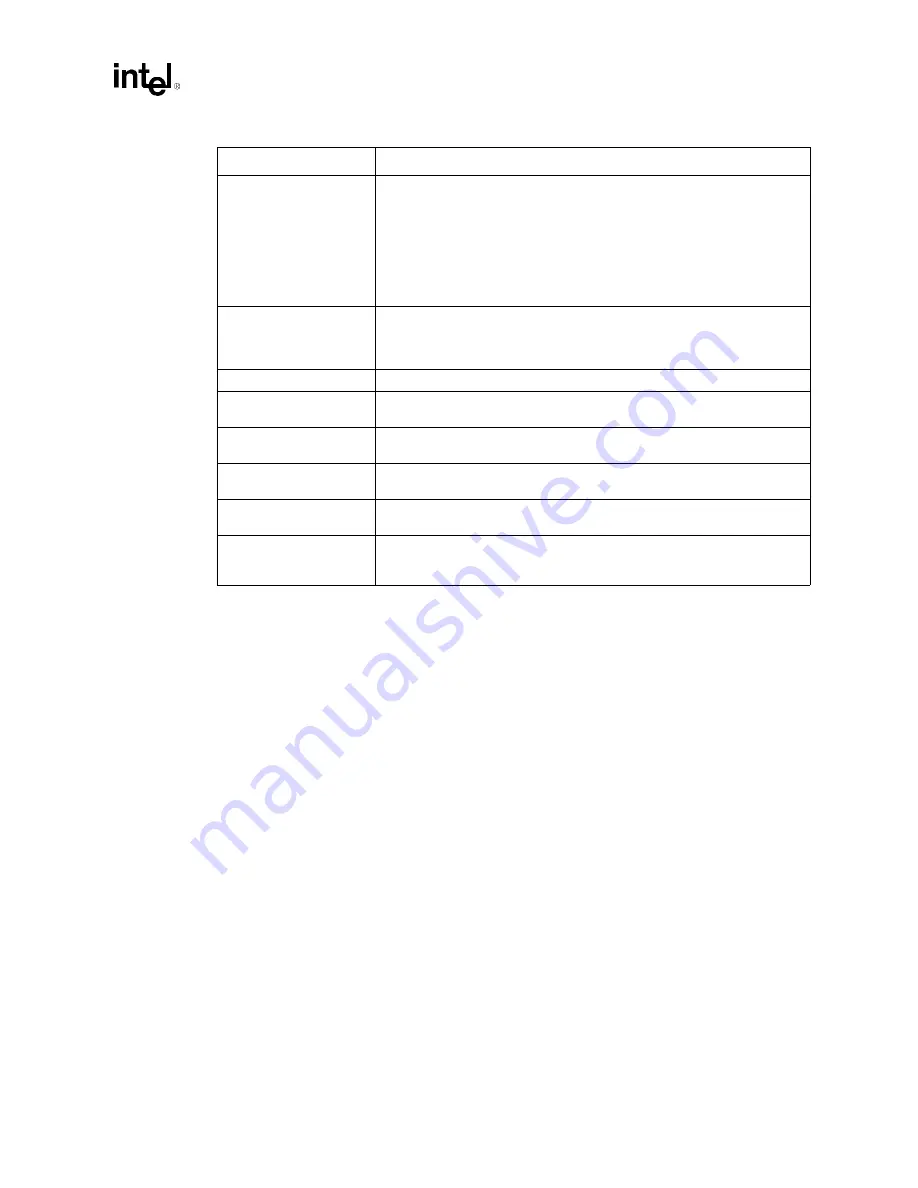

Simultaneous Switching

Output (SSO)

Effects which are differences in electrical timing parameters and degradation in

signal quality caused by multiple signal outputs simultaneously switching voltage

levels in the opposite direction from a single signal or in the same direction.

These are called odd mode and even mode switching, respectively. This

simultaneous switching of multiple outputs creates higher current swings that

may cause additional propagation delay (“push-out”) or a decrease in

propagation delay (“pull-in”). These SSO effects may impact the setup and/or

hold times and are not always taken into account by simulations. System timing

budgets should include margin for SSO effects.

Standby Power Rail

Standby power is supplied by the power supply during times when the system is

powered down. The purpose is to maintain functions that always need to be

enabled, such as the date and time-of-day within the BIOS. The power supply

provides a +5 VSB power rail.

Stub

The branch from the bus trunk terminating at the pad of an agent.

Trunk

The main connection, excluding interconnect branches, from one end agent pad

to the other end agent pad.

Undershoot

The minimum voltage extending below VSS observed for a signal at the device

pad.

VCC_CPU

VCC_CPU is the core power for the processor. The system bus is terminated to

VCC_CPU.

Victim

A network that receives a coupled crosstalk signal from another network is called

the victim network.

VRM 9.1

“VRM 9.1” refers to the Voltage Regulator Module specification for the Xeon

processor. It is a DC-DC converter module that supplies the required voltage and

current to a single processor.

Convention/Terminology

Description

Summary of Contents for Xeon

Page 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Page 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Page 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Page 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Page 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Page 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Page 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Page 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Page 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Page 222: ...Schematics 222 Design Guide This page is intentionally left blank ...