+VCC_CPU

+V3_3

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

+V3_3

+VCC_CPU

+

+

+VCC_CPU

+V3_3

A10

A11

A12

A13

A14

A15

A16

A17

A18

A19

A20

A21

A22

A23

A24

A25

A26

A27

A28

A29

A3

A30

A31

A32

A33

A34

A35

A4

A5

A6

A7

A8

A9

AP0

AP1

D0

D1

D10

D11

D12

D13

D14

D15

D16

D17

D18

D19

D2

D20

D21

D22

D23

D24

D25

D26

D27

D28

D29

D3

D30

D31

D32

D33

D34

D35

D36

D37

D38

D39

D4

D40

D41

D42

D43

D44

D45

D46

D47

D48

D49

D5

D50

D51

D52

D53

D54

D55

D56

D57

D58

D59

D6

D60

D61

D62

D63

D7

D8

D9

DBI0

DBI1

DBI2

DBI3

DP0

DP1

DP2

DP3

RE00

RE01

RE02

RE03

RE04

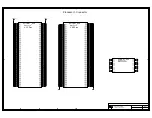

SOCKET_604

Part 1 of 5

+VCC_CPU

A20M

ADS

ADSTB0

ADSTB1

BCLK0

BCLK1

BINIT

BNR

BPM0

BPM1

BPM2

BPM3

BPM4

BPM5

BPRI

BR0

BR1

BR2

BR3

COMP0

COMP1

DBSY

DEFER

DRDY

DSTBN0

DSTBN1

DSTBN2

DSTBN3

DSTBP0

DSTBP1

DSTBP2

DSTBP3

FERR

GTLREF0

GTLREF1

GTLREF2

GTLREF3

HIT

HITM

IERR

IGGNE

INIT

LINT0

LINT1

LOCK

MCERR

ODTEN

PROCHOT

PWRGOOD

RESET

RS0

RS1

RS2

RSP

SKTOCC

SLP

SMI

SM_ALERT

SM_CLK

SM_DAT

SM_EP_A0

SM_EP_A1

SM_EP_A2

SM_TS_A0

SM_TS_A1

SM_VCC0

SM_VCC1

SM_WP

STPCLK

TCK

TD0

TDI

TESTHI0

TESTHI1

TESTHI3

TESTHI4

TESTHI5

TESTHI6

THERMTRIP

TMS

TRDY

TRST

VCCA

VCCIOPLL

VCCSENSE

VID0

VID1

VID2

VID3

VID4

VSSA

VSSSENSE

TESTHI2

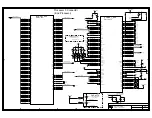

SOCKET_604

Part 2 of 5

CAD NOTE:

AB4, AD4, AA5

Caps close to pins

SMBUS Partition 2

CPU0 Thermal Sensor = 32

CPU0 IDROM = A2

Place BPM termination

Caps close to pins

F9, W9, F23, W23

resistors at ends of traces.

(Middle processor)

Processor 1 Connector

R8

4

1%

150

4,9

ITP_TDI_P1

51

R29

51

R22

R7

51

R27

51

51

R26

R25

51

51

R24

R23

51

CPU1_SKTOCC_N

7,80

F27

D19

F17

F14

Y4

W5

F11

F20

F6

F8

E7

F5

E8

E4

D23

D20

F12

E11

D10

AD16

E16

F18

C23

E18

Y21

Y18

Y15

Y12

Y20

Y17

Y14

Y11

E27

W23

W9

F23

F9

E22

A23

E5

C26

D6

B24

G23

A17

D7

B5

B25

AB7

Y8

E21

D22

F21

C6

A3

AE6

C27

AD28

AC28

AC29

AA29

AB29

AB28

AA28

Y29

AE28

AE29

AD29

D4

E24

E25

C24

W6

W7

Y6

AA7

AD5

AE5

F26

A25

E19

F24

AB4

AD4

B27

F3

E3

D3

C3

B3

AA5

D26

W8

J17

R2

1%

49.

9

CPU1_GTL_VREF2

4,9

CPU1_GTL_VREF1

4,9

A13

B16

B14

B13

A12

C15

C14

D16

D15

F15

A10

B10

B11

C12

E14

D13

A9

B8

E13

D12

A22

C11

B7

A6

A7

C9

C8

A20

B18

C18

A19

C17

D17

E10

D9

Y26

AA27

AA22

AA21

AB20

AB22

AB19

AA19

AE26

AC26

AD25

AE25

Y24

AC24

AD24

AE23

AC23

AA18

AC20

AC21

AE22

AE20

AD21

AA25

AD19

AB17

AB16

AA16

AC17

AE13

AD18

AB15

AD13

AD14

AD27

AD11

AC12

AE10

AC11

AE9

AD10

AD8

AC9

AA13

AA14

Y23

AC14

AB12

AB13

AA11

AA10

AB10

AC8

AD7

AE7

AC6

AA24

AC5

AA8

Y9

AB6

AB26

AB25

AB23

AC27

AD22

AE12

AB9

AC18

AE19

AC15

AE17

B19

B21

C21

C20

B22

J17

4

CPU1_VCCA

4

CPU1_VCCIOPLL

CPU1_VSSA

4

4,6,9

CPU_BPM0_N

51

R

1024

4,6,9

CPU_BPM1_N

R

1023

51

300

R

831

CPU_LINT1_NMI

6,9,80

4,6,9

CPU_BPM0_N

CPU_BPM1_N

4,6,9

4,6,9

CPU_BPM2_N

4,6,9

CPU_BPM3_N

CPU1_BREQ0_N

6

CPU_BPM2_N

4,6,9

CPU1_ODTEN

2

1

33UF

C

665

12

C

664

33UF

R

922

1K

100

R1

6

R1

3

1K

NO

P

O

P

CPU_BREQ2_3_N

6

9

ITP_TDO_P1

ITP_TDI_P1

4,9

CPU1_IERR_N

CPU1_COMP1

CPU1_COMP0

CPU1_GTL_VREF2

4,9

CPU1_GTL_VREF1

4,9

CPU1_TESTHI6

CPU1_TESTHI5

CPU1_TESTHI4

CPU1_TESTHI3

CPU1_TESTHI2

CPU1_TESTHI1

CPU1_TESTHI0

CPU1_VCCIOPLL

4

CPU1_VSSA

4

CPU1_VCCA

4

CPU1_VID4

CPU1_VID0

CPU1_VID1

CPU1_VID3

CPU1_VID[4:0]

60

CPU1_VID2

CPU1_SM_EP_A1

NO

P

O

P

1K

R2

1

1K

R1

2

CPU1_SM_TS_A0

CPU1_SM_TS_A1

CPU1_SM_EP_A0

CPU1_SM_EP_A2

CPU1_BCLK0

65

CPU1_BCLK1

65

CPU0_BREQ0_N

6,10

C

534

220P

F

C

536

220P

F

220P

F

C

537

680

R11

CPU_FERR_N

6,53

4,6

CPU_SMBUS_WP

4,6

CPU_SMBUS_WP

R1

49.

9

I2C_BUS2_DAT

6,11,80,81

I2C_BUS2_CLK

6,11,80,81

CPU_STPCLK_N

6,9,53

CPU1_SMI_N

9,80

R2

0

1K

NO

P

O

P

49.9

1%

R6

1

2

4.7UH

L4

2

1

L3

4.7UH

220P

F

C

535

R5

1%

49.9

NO

P

O

P

1K

R1

5

R

1

4

1K

NO

P

O

P

ITP_TRST_N

4,6,9

R1

7

1K

NO

P

O

P

NO

P

O

P

1K

R1

9

R

1

8

1K

NO

P

O

P

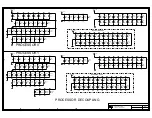

FSB_A[35:3]_N

6,10

FSB_A35_N

FSB_A3_N

FSB_A4_N

FSB_A5_N

FSB_A6_N

FSB_A7_N

FSB_A8_N

FSB_A9_N

FSB_A10_N

FSB_A11_N

FSB_A12_N

FSB_A13_N

FSB_A14_N

FSB_A15_N

FSB_A16_N

FSB_A17_N

FSB_A18_N

FSB_A19_N

FSB_A20_N

FSB_A21_N

FSB_A22_N

FSB_A23_N

FSB_A24_N

FSB_A25_N

FSB_A26_N

FSB_A27_N

FSB_A28_N

FSB_A29_N

FSB_A30_N

FSB_A31_N

FSB_A32_N

FSB_A33_N

FSB_A34_N

FSB_HD51_N

FSB_HD62_N

FSB_HD61_N

FSB_HD60_N

FSB_HD59_N

FSB_HD58_N

FSB_HD57_N

FSB_HD56_N

FSB_HD55_N

FSB_HD54_N

FSB_HD53_N

FSB_HD52_N

FSB_HD50_N

FSB_HD49_N

FSB_HD48_N

FSB_HD47_N

FSB_HD46_N

FSB_HD45_N

FSB_HD44_N

FSB_HD43_N

FSB_HD42_N

FSB_HD41_N

FSB_HD40_N

FSB_HD39_N

FSB_HD38_N

FSB_HD37_N

FSB_HD36_N

FSB_HD35_N

FSB_HD34_N

FSB_HD33_N

FSB_HD32_N

FSB_HD31_N

FSB_HD30_N

FSB_HD29_N

FSB_HD28_N

FSB_HD27_N

FSB_HD26_N

FSB_HD25_N

FSB_HD24_N

FSB_HD23_N

FSB_HD22_N

FSB_HD21_N

FSB_HD20_N

FSB_HD19_N

FSB_HD18_N

FSB_HD17_N

FSB_HD16_N

FSB_HD15_N

FSB_HD14_N

FSB_HD13_N

FSB_HD12_N

FSB_HD11_N

FSB_HD10_N

FSB_HD9_N

FSB_HD8_N

FSB_HD7_N

FSB_HD6_N

FSB_HD5_N

FSB_HD4_N

FSB_HD3_N

FSB_HD2_N

FSB_HD1_N

FSB_HD0_N

FSB_HD63_N

FSB_HD[63:0]_N

6,10

FSB_HREQ0_N

FSB_HREQ1_N

FSB_HREQ2_N

FSB_HREQ3_N

FSB_HREQ[4:0]_N

6,10

FSB_HREQ4_N

FSB_DBI0_N

FSB_DBI1_N

FSB_DBI2_N

FSB_DBI3_N

FSB_DBI[3:0]_N

6,10

FSB_AP1_N

6,10

FSB_AP0_N

6,10

FSB_DP2_N

FSB_DP0_N

FSB_DP1_N

FSB_DP[3:0]_N

6,10

FSB_DP3_N

FSB_ADS_N

6,10

FSB_BINIT_N

6,10

FSB_BNR_N

6,10

CPU_BPM5_N

4,6,9

CPU_BPM4_N

4,6,9

FSB_DBSY_N

6,10

FSB_DRDY_N

6,10

FSB_HIT_N

6,10

FSB_HITM_N

6,10

FSB_HLOCK_N

6,10

FSB_BERR_N

6,10

FSB_ADSTB[1:0]_N

6,10

FSB_ADSTB1_N

FSB_ADSTB0_N

FSB_DSTBP[3:0]_N

6,10

FSB_DSTBP0_N

FSB_DSTBP1_N

FSB_DSTBP2_N

FSB_DSTBP3_N

FSB_DSTBN3_N

FSB_DSTBN2_N

FSB_DSTBN0_N

FSB_DSTBN[3:0]_N

6,10

FSB_DSTBN1_N

CPU_THRM_TRIP_N

6,7

CPU_PROC_HOT_N

6,80

CPU_SMBALERT_N

6

ITP_TRST_N

4,6,9

ITP_TMS_P

6,9

ITP_TCK_P

6,9

ICH3_CPUSLP_N

6,9,53

ICH3_CPUPWRGD

6,53

ICH3_LINT0_INTR

6,9,53

ICH3_INIT_N

6,9,53,66

ICH3_IGNNE_N

6,9,53

ICH3_A20M_N

6,9,53

FSB_HTRDY_N

6,10

FSB_RSP_N

6,10

FSB_RS0_N

FSB_RS[2:0]_N

6,10

FSB_RS2_N

FSB_RS1_N

FSB_CPURST_N

6,9,10

FSB_DEFER_N

6,10

FSB_BPRI_N

6,10

NO

P

O

P

1K

R

921

R5

3

51

51

R5

6

R5

7

51

51

R3

5

CPU_BPM5_N

4,6,9

CPU_BPM3_N

4,6,9

CPU_BPM4_N

4,6,9

4

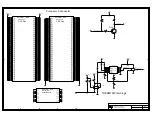

Summary of Contents for Xeon

Page 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Page 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Page 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Page 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Page 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Page 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Page 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Page 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Page 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Page 222: ...Schematics 222 Design Guide This page is intentionally left blank ...