+V1_2

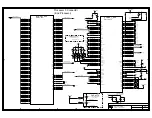

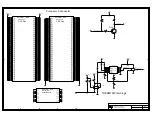

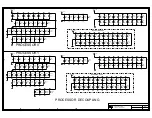

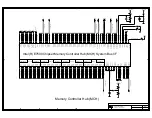

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

+V2_5

+VCC_CPU

+V1_2

+VCC_CPU

+V1_2

+V2_5

+V2_5

+VCC_CPU

+

+

+

+V1_2

+V1_2

+V1_2

L20

V

C

C

1_2_13

V

C

C

A

1_2_7

V

C

C

A

1_2_6

V

C

C

A

1_2_5

V

C

C

2_5_77

V

C

C

2_5_76

V

C

C

2_5_75

V

C

C

2_5_74

V

C

C

2_5_71

V

C

C

2_5_70

V

C

C

2_5_69

V

C

C

2_5_68

V

C

C

2_5_67

V

C

C

2_5_66

V

C

C

2_5_65

V

C

C

2_5_64

V

C

C

2_5_62

V

C

C

2_5_61

V

C

C

2_5_60

V

C

C

2_5_59

V

C

C

2_5_58

V

C

C

2_5_57

V

C

C

2_5_56

V

C

C

2_5_55

V

CC_

CP

U_

3

0

V

CC_

CP

U_

2

5

V

CC_

CP

U_

2

4

V

CC_

CP

U_

2

3

V

CC_

CP

U_

2

2

V

CC_

CP

U_

2

1

V

CC_

CP

U_

2

0

V

CC_

CP

U_

1

9

V

CC_

CP

U_

1

8

V

CC_

CP

U_

1

7

V

CC_

CP

U_

1

6

V

CC_

CP

U_

1

5

V

CC_

CP

U_

1

4

V

CC_

CP

U_

1

3

V

C

C

1_2_46

V

C

C

1_2_38

V

C

C

2_5_52

V

C

C

2_5_51

V

C

C

2_5_50

V

C

C

2_5_48

V

C

C

2_5_47

V

C

C

2_5_46

V

C

C

2_5_45

V

C

C

2_5_44

V

C

C

2_5_43

V

C

C

2_5_42

V

C

C

2_5_41

V

C

C

2_5_40

V

C

C

2_5_39

V

C

C

2_5_38

V

C

C

2_5_37

V

C

C

2_5_36

V

C

C

2_5_35

V

C

C

2_5_34

V

C

C

2_5_33

V

C

C

2_5_32

V

C

C

2_5_31

V

C

C

2_5_30

V

C

C

2_5_29

V

C

C

2_5_28

V

C

C

2_5_27

V

C

C

2_5_26

V

C

C

2_5_25

V

C

C

2_5_24

V

C

C

2_5_23

V

C

C

2_5_22

V

C

C

2_5_21

V

C

C

2_5_20

V

C

C

2_5_19

V

C

C

2_5_18

V

C

C

2_5_17

V

C

C

2_5_16

V

C

C

2_5_15

V

C

C

2_5_14

V

C

C

2_5_13

V

C

C

2_5_12

V

C

C

2_5_11

V

C

C

2_5_10

V

C

C

2_5_9

V

C

C

2_5_8

V

C

C

2_5_7

V

C

C

2_5_6

V

C

C

2_5_5

V

C

C

2_5_4

V

C

C

2_5_3

V

CC_

CP

U_

3

8

V

CC_

CP

U_

3

7

V

CC_

CP

U_

3

6

V

CC_

CP

U_

3

5

V

CC_

CP

U_

3

4

V

CC_

CP

U_

3

3

V

CC_

CP

U_

3

2

V

C

C

1_2_51

V

C

C

1_2_50

V

C

C

1_2_49

V

C

C

1_2_48

V

C

C

1_2_47

V

C

C

1_2_44

V

C

C

1_2_43

V

C

C

A

1_2_3

V

C

C

A

1_2_2

V

C

C

A

1_2_1

V

C

C

1_2_34

V

C

C

1_2_33

V

C

C

1_2_32

V

C

C

1_2_27

V

C

C

1_2_26

V

C

C

1_2_23

V

C

C

1_2_21

V

C

C

1_2_20

V

C

C

1_2_19

V

C

C

1_2_18

V

C

C

1_2_12

V

C

C

1_2_11

V

CC_

CP

U_

1

1

V

CC_

CP

U_

1

0

V

CC_

CP

U_

9

V

CC_

CP

U_

8

V

CC_

CP

U_

7

V

CC_

CP

U_

6

V

CC_

CP

U_

5

V

CC_

CP

U_

4

V

CC_

CP

U_

3

V

CC_

CP

U_

2

V

C

C

1_2_36

V

C

C

1_2_37

V

C

C

1_2_45

V

C

C

1_2_52

V

CC_

CP

U_

3

9

V

CC_

CP

U_

1

2

V

CC_

CP

U_

2

6

V

CC_

CP

U_

2

7

V

CC_

CP

U_

2

8

V

CC_

CP

U_

2

9

V

CC_

CP

U_

3

1

V

C

C

1_2_1

V

C

C

1_2_2

V

C

C

1_2_3

V

C

C

1_2_4

V

C

C

1_2_7

V

C

C

1_2_8

V

C

C

1_2_24

V

C

C

1_2_9

V

C

C

1_2_10

V

C

C

1_2_15

V

C

C

1_2_16

V

C

C

1_2_17

V

C

C

1_2_28

V

C

C

1_2_53

V

C

C

1_2_5

V

C

C

1_2_6

V

C

C

2_5_1

V

C

C

2_5_2

V

C

C

2_5_49

V

C

C

2_5_53

V

C

C

2_5_54

V

C

C

2_5_63

V

C

C

2_5_72

V

C

C

2_5_73

V

C

C

1_2_31

V

C

C

A

1_2_4

V

CC_

CP

U_

1

V

CCA

CP

U1

_

2

V

CCA

HI1

_

2

V

C

C

1_2_14

VCC1_2

VCC2_5

VCC_CPU

MCH power

Y3

2

VSS1

0

5

VSS2

7

2

VSS1

VSS1

0

VSS1

0

0

VSS1

0

1

VSS1

0

2

VSS1

0

3

VSS1

0

4

VSS1

0

7

VSS1

0

8

VSS1

0

9

VSS1

1

VSS1

1

0

VSS1

1

1

VSS1

1

2

VSS1

1

3

VSS1

1

4

VSS1

1

5

VSS1

1

6

VSS1

1

7

VSS1

1

8

VSS1

1

9

VSS1

2

VSS1

2

0

VSS1

2

1

VSS1

2

2

VSS1

2

3

VSS1

2

4

VSS1

2

5

VSS1

2

6

VSS1

2

7

VSS1

2

8

VSS1

2

9

VSS1

3

VSS1

3

0

VSS1

3

1

VSS1

3

2

VSS1

3

3

VSS1

3

4

VSS1

3

5

VSS1

3

6

VSS1

3

7

VSS1

3

8

VSS1

3

9

VSS1

4

VSS1

4

0

VSS1

4

1

VSS1

4

2

VSS1

4

3

VSS1

4

4

VSS1

4

5

VSS1

4

6

VSS1

4

7

VSS1

4

8

VSS1

4

9

VSS1

5

VSS1

5

0

VSS1

5

1

VSS1

5

2

VSS1

5

3

VSS1

5

4

VSS1

5

5

VSS1

5

6

VSS1

5

7

VSS1

5

8

VSS1

5

9

VSS1

6

VSS1

6

0

VSS1

6

1

VSS1

6

2

VSS1

6

3

VSS1

6

4

VSS1

6

5

VSS1

6

6

VSS1

6

7

VSS1

6

8

VSS1

6

9

VSS1

7

VSS1

7

0

VSS1

7

1

VSS1

7

2

VSS1

7

3

VSS1

7

4

VSS1

7

5

VSS1

7

6

VSS1

7

7

VSS1

7

8

VSS1

7

9

VSS1

8

VSS1

8

0

VSS1

8

1

VSS1

8

2

VSS1

8

3

VSS1

8

4

VSS1

8

5

VSS1

8

6

VSS1

8

7

VSS1

8

8

VSS1

8

9

VSS1

9

VSS1

9

0

VSS1

9

1

VSS1

9

2

VSS1

9

3

VSS1

9

4

VSS1

9

5

VSS1

9

6

VSS1

9

7

VSS1

9

8

VSS1

9

9

VSS2

VSS2

0

VSS2

0

0

VSS2

0

1

VSS2

0

2

VSS2

0

3

VSS2

0

4

VSS2

0

5

VSS2

0

6

VSS2

0

7

VSS2

0

8

VSS2

0

9

VSS2

1

VSS2

1

0

VSS2

1

1

VSS2

1

2

VSS2

1

3

VSS2

1

4

VSS2

1

5

VSS2

1

6

VSS2

1

7

VSS2

1

8

VSS2

1

9

VSS2

2

VSS2

2

0

VSS2

2

1

VSS2

2

2

VSS2

2

3

VSS2

2

4

VSS2

2

5

VSS2

2

6

VSS2

2

7

VSS2

2

8

VSS2

2

9

VSS2

3

VSS2

3

0

VSS2

3

1

VSS2

3

2

VSS2

3

3

VSS2

3

4

VSS2

3

5

VSS2

3

6

VSS2

3

7

VSS2

3

8

VSS2

3

9

VSS2

4

VSS2

4

0

VSS2

4

1

VSS2

4

2

VSS2

4

3

VSS2

4

4

VSS2

4

5

VSS2

4

6

VSS2

4

7

VSS2

4

8

VSS2

4

9

VSS2

5

VSS2

5

0

VSS2

5

1

VSS2

5

2

VSS2

5

3

VSS2

5

4

VSS2

5

5

VSS2

5

6

VSS2

5

7

VSS2

5

8

VSS2

5

9

VSS2

6

VSS2

6

0

VSS2

6

1

VSS2

6

2

VSS2

6

3

VSS2

6

4

VSS2

6

5

VSS2

6

6

VSS2

6

7

VSS2

6

8

VSS2

6

9

VSS2

7

VSS2

7

0

VSS2

7

1

VSS2

7

3

VSS2

7

4

VSS2

7

5

VSS2

7

6

VSS2

7

7

VSS2

7

8

VSS2

7

9

VSS2

8

VSS2

8

0

VSS2

8

1

VSS2

8

2

VSS2

8

3

VSS2

8

4

VSS2

8

5

VSS2

8

6

VSS2

8

7

VSS2

8

8

VSS2

8

9

VSS2

9

VSS2

9

0

VSS2

9

1

VSS2

9

2

VSS2

9

3

VSS2

9

4

VSS2

9

5

VSS2

9

6

VSS2

9

7

VSS2

9

8

VSS2

9

9

VSS3

VSS3

0

VSS3

0

0

VSS3

1

VSS3

2

VSS3

3

VSS3

4

VSS3

5

VSS3

6

VSS3

7

VSS3

8

VSS3

9

VSS4

VSS4

0

VSS4

1

VSS4

2

VSS4

3

VSS4

4

VSS4

5

VSS4

6

VSS4

7

VSS4

8

VSS4

9

VSS5

VSS5

0

VSS5

1

VSS5

2

VSS5

3

VSS5

4

VSS5

5

VSS5

6

VSS5

7

VSS5

8

VSS5

9

VSS6

VSS6

0

VSS6

1

VSS6

2

VSS6

3

VSS6

4

VSS6

5

VSS6

6

VSS6

7

VSS6

8

VSS6

9

VSS7

VSS7

0

VSS7

1

VSS7

2

VSS7

3

VSS7

4

VSS7

5

VSS7

6

VSS7

7

VSS7

8

VSS7

9

VSS8

VSS8

0

VSS8

1

VSS8

2

VSS8

3

VSS8

4

VSS8

5

VSS8

6

VSS8

7

VSS8

8

VSS8

9

VSS9

VSS9

0

VSS9

1

VSS9

2

VSS9

3

VSS9

4

VSS9

5

VSS9

6

VSS9

7

VSS9

8

VSS9

9

VSS1

0

6

MCH VSS (ground) pins

Near Hub interface

Backside caps near center of MCH

Place caps near DDR interface

Near FSB interface

MCH

AJ

8

AK9

F2

8

A7

AA2

4

AA3

0

AB2

3

AB2

8

AC

1

AC

1

2

AC

1

4

AC

1

6

AG

6

AC

1

8

AC

2

0

AC

2

2

AC

2

4

AC

2

6

AC

3

2

AC

3

3

AD

1

1

AD

1

3

AD

1

5

AH

7

AD

1

7

AD

1

9

AD

2

1

AD

2

3

AD

2

6

AD

3

0

AE2

9

AE9

AF

1

0

AF

1

1

AH

4

AF

1

4

AF

1

7

AF

2

0

AF

2

6

AF

2

9

AF

3

2

AG

1

6

AG

2

5

AG

3

1

AH

1

2

AL

4

AH

1

5

AH

1

8

AH

2

1

AH

2

4

AH

2

7

AH

3

0

AJ

3

2

AJ

3

3

AK1

3

AK1

6

AJ

2

AK2

2

AK2

5

AK2

8

AK3

1

A

L12

A

L18

A

L21

A

L27

A

L30

A

L33

AK3

AM

1

1

AM

1

4

AM

1

7

AM

2

0

AM

2

3

AM

2

6

AM

2

9

AN

1

1

AN

1

5

AN

1

9

AD

6

AN

2

3

AN

2

7

AN

3

AN

3

1

AN

6

B1

0

B1

3

B1

6

B1

9

B2

2

AK6

B2

6

B2

9

B4

B7

C1

C1

2

C1

5

C2

1

C2

7

C3

0

AL

7

C3

3

C6

C9

D1

1

D1

4

D1

7

D2

0

D2

3

D3

1

D8

AM

8

AM

5

E2

5

E3

2

F1

2

F1

5

F1

8

F2

1

F2

7

F3

0

F6

F9

AF

2

G1

G11

G14

G17

G20

G23

G28

G31

G33

G8

AD

3

H1

0

H1

3

H1

6

H2

2

H2

6

H3

2

H8

J1

2

J1

5

J1

8

AG

1

J2

1

J2

4

J2

7

J3

0

J9

K1

2

K1

4

K1

6

K1

8

K2

0

AK1

K2

2

K2

8

N5

L1

L24

L32

L33

M2

3

M2

7

M3

0

U9

N2

4

N2

8

N3

1

P1

5

P1

7

P1

9

P2

3

P3

2

R1

R1

4

E2

R1

8

R2

0

R2

4

R2

7

R3

0

R3

3

R9

T1

5

T1

7

T1

9

H2

T2

3

T2

8

U1

4

U1

6

U1

8

U2

0

U2

4

U3

2

U8

K4

V1

5

V1

7

V1

9

V2

3

V2

7

V3

0

V9

W1

W1

4

W1

6

J3

W1

8

W2

0

W2

4

W2

8

W3

1

W3

3

Y1

5

Y1

7

Y1

9

Y2

3

AC

8

K8

Y2

6

L8

G4

M6

P2

M3

M9

P8

N9

U2

G7

R6

T4

V6

W4

W2

Y2

AA3

AA6

Y8

J1

9

D3

0

J2

0

G19

E5

J2

3

AB5

D4

AE4

AC

2

AG

9

L9

AF

8

C2

8

B2

7

AB4

AB7

AD

9

AA1

1

AB1

0

AC

1

1

AD

1

0

AN

9

AA9

M1

0

M5

N1

1

P1

0

R1

1

T1

0

U1

1

V1

0

W1

1

Y1

0

J6

B2

J1

7

K1

0

L11

L13

L15

L17

L19

L21

R1

6

V3

AC

2

9

AJ

1

0

D2

5

A1

1

A1

5

A1

9

A2

3

A2

9

A3

A3

1

U6

6

V2

0

T2

0

P2

0

T3

1

K3

1

AB3

1

R2

3

L26

L23

K2

4

H2

9

G27

E2

9

D3

3

B3

2

AM

3

2

AJ

2

9

AJ

2

6

AG

2

8

AF

2

3

AD

2

4

AD

2

2

AC

2

3

L10

AA1

0

E7

A6

Y1

T1

M1

H1

D1

AD

1

K9

AE7

Y5

U5

V1

4

W1

9

Y3

3

Y2

9

Y2

4

V2

4

U2

9

U2

3

T3

3

T2

4

P2

9

P2

4

M3

3

L29

H3

3

AN

7

AN

4

AN

2

6

AN

2

2

AN

1

8

AN

1

4

AN

1

0

A

L24

A

L15

AL

1

AK8

AK3

3

AK1

0

AJ

2

3

AJ

2

0

AJ

1

7

AJ

1

4

AJ

1

1

AG

2

2

AG

1

9

AG

1

3

AF

3

3

AE3

0

AE1

0

AD

3

3

AD

2

9

AD

2

5

AD

2

0

AD

1

8

AD

1

6

AD

1

4

AD

1

2

AC

1

9

AC

1

7

AC

1

5

AC

1

3

W1

0

V1

1

U1

0

T1

1

R1

0

P1

1

N1

0

L14

L12

K1

1

H1

9

E2

6

A3

0

A2

6

Y1

8

Y1

6

Y1

4

V1

8

V1

6

U1

9

T1

6

T1

4

R1

7

P1

8

P1

4

K2

3

K2

1

E2

2

E1

9

H5

W7

R3

P5

F3

K7

AH

1

AF

5

AJ

5

AG

3

W1

5

W1

7

R1

5

L16

Y1

1

L5

AB1

1

AC

1

0

C3

D5

M1

1

B2

8

H2

0

A1

0

A1

4

A2

2

E1

0

R1

9

E1

3

E1

6

K1

3

K1

5

K1

7

K1

9

T1

8

L18

A1

8

L22

AA2

3

AA2

7

W2

3

AB2

4

AC

2

1

AN

3

0

M2

4

N2

3

U1

7

Y2

0

AC

5

U1

5

P1

6

U6

6

L

O

W

ESL

0.

1U

F

C

1644

C

1643

0.

1U

F

L

O

W

ESL

L

O

W

ESL

0.

1U

F

C

1498

C

1497

0.

1U

F

L

O

W

ESL

14

VCCACPU1_2

L

O

W

ESL

0.

1U

F

C

1496

C

1499

0.

1U

F

L

O

W

ESL

VCCA_HI_FILT

1

R764

VCCA_CPU_FILT

1

2

L20

0.1UH

14

VCCACPU1_2

C

798

0.

1U

F

C

785

0.

1U

F

2

1

L19

54NH

0.

1U

F

C

723

C

726

0.

1U

F

0.

1U

F

C

722

0.

1U

F

C

716

0.

1U

F

C

714

C

825

0.

1U

F

C

824

0.

1U

F

0.

1U

F

C

823

C

822

0.

1U

F

0.

1U

F

C

821

C

820

0.

1U

F

0.

1U

F

C

819

C

818

0.

1U

F

0.

1U

F

C

817

C

816

0.

1U

F

0.

1U

F

C

815

C

814

0.

1U

F

0.

1U

F

C

813

C

812

0.

1U

F

0.

1U

F

C

811

C

810

0.

1U

F

0.

1U

F

C

809

C

808

0.

1U

F

0.

1U

F

C

807

C

806

0.

1U

F

0.

1U

F

C

805

C

804

0.

1U

F

0.

1U

F

C

803

C

802

0.

1U

F

0.

1U

F

C

801

C

800

0.

1U

F

0.

1U

F

C

799

0.

1U

F

C

797

C

796

0.

1U

F

0.

1U

F

C

795

C

794

0.

1U

F

0.

1U

F

C

793

C

792

0.

1U

F

0.

1U

F

C

791

C

790

0.

1U

F

0.

1U

F

C

789

C

788

0.

1U

F

0.

1U

F

C

787

0.

1U

F

C

786

R763

1

2

1

100U

F

C

1590

L

O

W

ESL

12

L

O

W

ESL

C

1591

100U

F

2

1

100U

F

C

1592

L

O

W

ESL

2

1

L21

0.1UH

C

713

0.

1U

F

C

715

0.

1U

F

C

717

0.

1U

F

C

721

0.

1U

F

0.

1U

F

C

720

C

719

0.

1U

F

0.

1U

F

C

718

0.

1U

F

C

727

0.

1U

F

C

725

C

724

0.

1U

F

VCCAHI1_2

14

VCCAHI1_2

14

14

VCCA1_2

VCCA1_2

14

14

Summary of Contents for Xeon

Page 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Page 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Page 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Page 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Page 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Page 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Page 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Page 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Page 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Page 222: ...Schematics 222 Design Guide This page is intentionally left blank ...