F

D

P

7045L

S

D

G

F

D

P

7045L

S

D

G

F

D

P

6670A

L

S

D

G

F

D

P

6670A

L

S

D

G

+V12

1.9UH

+VCC_CPU

BAT54C

+V12

HIP6601

UGATE

BOOT

PWM

GND

PHASE

PVCC

VCC

LGATE

+VCC_CPU

BAT54C

+V12

HIP6601

UGATE

BOOT

PWM

GND

PHASE

PVCC

VCC

LGATE

BAT54C

+V12

+V5_0

+VCC_CPU

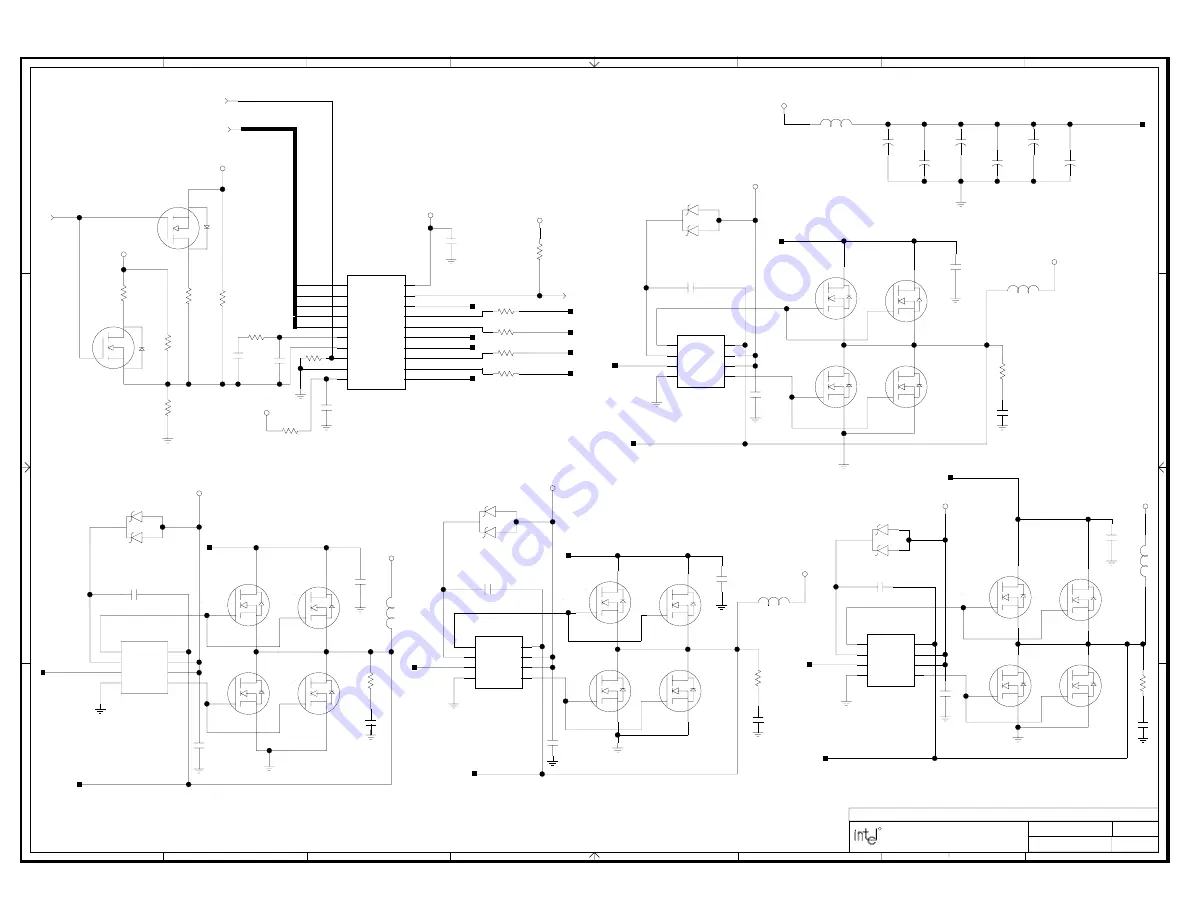

INTEL(R) E7500 CHIPSET CUSTOMER REFERENCE SCHEMATICS

R

D

C

B

B

D

C

1

1

2

3

4

5

6

7

8

2

3

4

5

6

7

8

A

A

LAST REVISED:

1900 Prairie City Road

Folsom, California 095630

TITLE:

Platform Apps Engineering

SHEET

03/04/02

HIP6601

UGATE

BOOT

PWM

GND

PHASE

PVCC

VCC

LGATE

+V3_3

HIP6601

UGATE

BOOT

PWM

GND

PHASE

PVCC

VCC

LGATE

+V12

BAT54C

270U

F

+

270U

F

+

270U

F

+

270U

F

+

270U

F

+

270U

F

+

+VCC_CPU

+V5_0

BSS1

3

8

S

D

G

+VCC_CPU

BSS1

3

8

S

D

G

F

D

P

6670A

L

S

D

G

F

D

P

6670A

L

S

D

G

F

D

P

7045L

S

D

G

F

D

P

7045L

S

D

G

F

D

P

6670A

L

S

D

G

F

D

P

6670A

L

S

D

G

F

D

P

7045L

S

D

G

F

D

P

7045L

S

D

G

F

D

P

6670A

L

S

D

G

F

D

P

6670A

L

S

D

G

F

D

P

7045L

S

D

G

F

D

P

7045L

S

D

G

HIP6311

VSEN

FS_DIS

FB

COMP

VID0

VID1

VID2

VID3

VID4

PGOOD

PWM4

ISEN4

ISEN1

PWM1

PWM2

ISEN2

ISEN3

PWM3

VCC

GND

+VCC_CPU

400NH

400N

H

400NH

400N

H

Processor Voltage Regulator circuitry

CPU0_VID0

CPU0_VID4

CPU0_VID3

CPU0_VID2

CPU0_VID1

CPU0_VID[4:0]

6,60

12

L15

2

1

L14

12

L16

2

1

L13

100P

F

C

1512

NO

P

O

P

6301_ISEN2

61

C1511

100PF

NOPOP

100P

F

C

1510

NO

P

O

P

C1509

100PF

NOPOP

10

8

7

6

5

4

3

2

1

19

18

17

16

15

14

13

12

11

20

9

U55

0.1UF

C514

NOPOP

C513

0.1UF

DP_MODE_5V

60

C458

1UF

1

2

3

Q63

3

2

1

Q28

1

2

3

Q58

3

2

1

Q27

6301_PWM3

61

1U

F

C

1571

C1572

1UF

C

1574

1U

F

1UF

C459

1

2

3

Q24

3

2

1

Q62

3

2

1

Q57

1

2

3

Q23

6301_ISEN4

61

4

NO

P

O

P

R

737

1

2

3

Q61

3

2

1

Q29

1

2

3

Q56

3

2

1

Q22

6301_ISEN1

61

1

3

2

Q55

6311_FB

6311_COMP

R

736

NOPOP

4

6301_PWM1

61

1%

R

1014

1.

96K

2

3

1

Q54

2.

61K

1%

R

476

C

512

2200P

F

392K

R

480

1%

0

R478

4.3K

R823

VRD_OFF_N

60

61

6301_PWM3

61

6301_PWM2

61

6301_PWM1

61

6301_PWM4

1UF

C1573

R

714

10K

0.1UF

C518

C517

0.1UF

0.1UF

C516

C515

0.1UF

C457

1UF

1UF

C456

2

1

C

1443

2

1 C

1445

2

1

C

1447

12

C

1446

12

C

1444

12

C

1442

1

3

2

CR37

6301_ISEN3_R

6301_ISEN2_R

6301_ISEN4_R

6301_ISEN1_R

6301_ISEN3

61

6301_ISEN2

61

4.3K

R821

R822

4.3K

R820

4.3K

6301_ISEN4

61

6301_PWM4

61

4

3

2

1

8

7

6

5

U48

6301_PWM2

61

ICH3_VRMPWRGD

55

R477

1%

121K

5

6

7

8

1

2

3

4

U51

5%

NOPOP

R

481

2K

R479

15K

C455

120PF

2

3

1

CR40

4

3

2

1

8

7

6

5

U50

1

3

2

CR39

5

6

7

8

1

2

3

4

U49

2

3

1

CR38

2

1

L17

R

738

NOPOP

4

4

NO

P

O

P

R

739

61

6301_ISEN1

COIL_P12V_CPU

61

1%

R

1015

340K

COIL_P12V_CPU

61

61

COIL_P12V_CPU

COIL_P12V_CPU

61

1

2

3

Q25

3

2

1

Q59

1

2

3

Q26

3

2

1

Q64

61

6301_ISEN3

61

COIL_P12V_CPU

61

Summary of Contents for Xeon

Page 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Page 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Page 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Page 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Page 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Page 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Page 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Page 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Page 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Page 222: ...Schematics 222 Design Guide This page is intentionally left blank ...