Design Guide

71

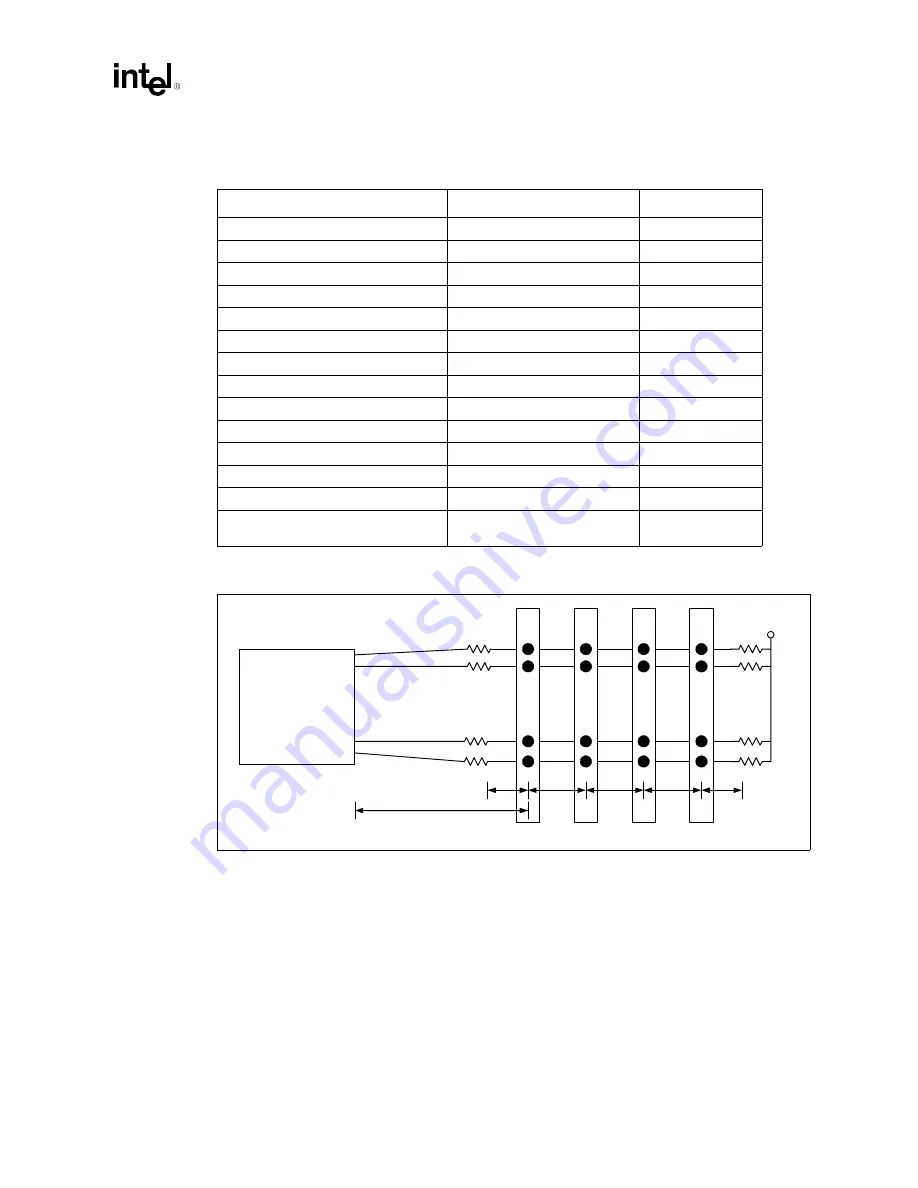

Memory Interface Routing Guidelines

NOTES:

1. Indicated lengths measure from the MCH pin to the DIMM connector pin (including the series resistor).

Table 6-3. Source Synchronous Signal Group Routing Guidelines

Parameter

Intel

®

E7500

Reference

Signal Group

DQ[63:0], CB[7:0], DQS[17:0]

Topology

Daisy Chain

Reference Plane

Ground

MCH to Rtt (Zo)

50

Ω

± 10%

MCH to Rtt Trace Width

5 mil

Nominal Trace Spacing

15 mil

Trace Length – MCH to DIMM1

1.8” to 6.0”

Trace Length – Rs to DIMM1

< 0.8”

Trace Length – DIMM to DIMM

0.8” to 1.2”

Trace Length – DIMM to Rtt

< 0.8”

Series Resistor (Rs)

10

Ω

± 2%

Termination Resistor (Rtt)

22

Ω

± 2%

MCH Breakout Guidelines

5/5, < 500 mil

Length Tuning Requirements

DQ to DQS: ± 100 mil

DQS to CMDCLK pair: ± 1750 mil

Figure 6-4. Source Synchronous Topology

DIMMs

DQ/CB Data Group

Associated DQS

DQ/CB Data Group

Associated DQS

MCH

DIMM to

DIMM

DDR VTERM

(1.25V)

Intel

®

MCH to DIMM1

Rs

Rs

Rs

Rs

Rtt

Rtt

Rtt

Rtt

Rs to

DIMM1

DIMM to

DIMM

DIMM to

DIMM

DIMM

to Rtt

Summary of Contents for Xeon

Page 24: ...Introduction 24 Design Guide This page is intentionally left blank ...

Page 30: ...Component Quadrant Layout 30 Design Guide This page is intentionally left blank ...

Page 52: ...Platform Clock Routing Guidelines 52 Design Guide This page is intentionally left blank ...

Page 66: ...System Bus Routing Guidelines 66 Design Guide This page is intentionally left blank ...

Page 118: ...Intel 82870P2 P64H2 118 Design Guide This page is intentionally left blank ...

Page 146: ...I O Controller Hub 146 Design Guide This page is intentionally left blank ...

Page 148: ...Debug Port 148 Design Guide This page is intentionally left blank ...

Page 210: ...Schematic Checklist 210 Design Guide This page is intentionally left blank ...

Page 220: ...Layout Checklist 220 Design Guide This page is intentionally left blank ...

Page 222: ...Schematics 222 Design Guide This page is intentionally left blank ...